8

Enter keyword

# Flip Flops

A digital computer needs devices which can store information. A flip flop is a binary storage device. It can store binary bit either 0 or 1. It has two stable states HIGH and LOW i.e. 1 and 0. It has the property to remain in one state indefinitely until it is directed by an input signal to switch over to the other state. It is also called bistable multivibrator.

The basic formation of flip flop is to store data. They can be used to keep a record or what value of variable (input, output or intermediate). Flip flop are also used to exercise control over the functionality of a digital circuit i.e. change the operation of a circuit depending on the state of one or more flip flops. These devices are mainly used in situations which require one or more of these three.

Operations, storage and sequencing.

### Latch Flip Flop

The R-S (Reset Set) flip flop is the simplest flip flop of all and easiest to understand. It is basically a device which has two outputs one output being the inverse or complement of the other, and two inputs. A pulse on one of the inputs to take on a particular logical state. The outputs will then remain in this state until a similar pulse is applied to the other input. The two inputs are called the Set and Reset input (sometimes called the preset and clear inputs).

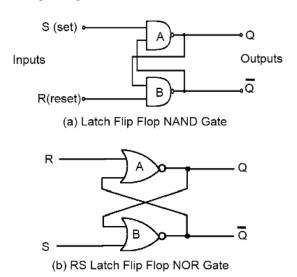

Such flip flop can be made simply by cross coupling two inverting gates either NAND or NOR gate could be used Figure 1(a) shows on RS flip flop using NAND gate and Figure 1(b) shows the same circuit using NOR gate.

Figure 1: Latch R-S Flip Flop Using NAND and NOR Gates

To describe the circuit of Figure 1(a), assume that initially both R and S are at the logic 1 state and that output is at the logic 0 state.

Now, if Q = 0 and R = 1, then these are the states of inputs of gate B, therefore the outputs of gate B is at 1 (making it the inverse of Q i.e. 0). The output of gate B is connected to an input of gate A so if S = 1, both inputs of gate A are at the logic 1 state. This means that the output of gate A must be 0 (as was originally specified). In other words, the 0 state at Q is continuously disabling gate B so that any change in R has no effect. Also the 1 state at  $\overline{Q}$  is continuously enabling gate A so that any change S will be transmitted through to Q. The above conditions constitute one of the stable states of the device referred to as the Reset state since Q = 0.

Now suppose that the R-S flip flop in the Reset state, the S input goes to 0. The output of gate A i.e. Q will go to 1 and with Q = 1 and R = 1, the output of gates B  $(\overline{Q})$  will go to 0 with  $\overline{Q}$  now 0 gate A is disabled keeping Q at 1. Consequently, when S returns to the 1 state it has no effect on the flip flop whereas a change in R will cause a change in the output of gate B. The above conditions constitute the other stable state of the device, called the Set state since Q = 1. Note that the change of the state of S from 1 to 0 has caused the flip flop to change from the Reset state to the Set state.

There is another input condition which has not yet been considered. That is when both the R and S inputs are taken to the logic state 0. When this happens both Q and  $\overline{Q}$ will be forced to 1 and will remain so far as long as R and S are kept at 0. However when both inputs return to 1 there is no way of knowing whether the flip flop will latch in the Reset state or the Set state. The condition is said to be indeterminate because of this indeterminate state great care must be taken when using R-S flip flop to ensure that both inputs are not instructed simultaneously.

Table 1: The truth table for the NAND R-S flip flop

| Initial<br>Conditions | Inputs<br>(Pulsed) |   | Final Output  |   |

|-----------------------|--------------------|---|---------------|---|

| Q                     | s                  | R | Q             | Q |

| 1                     | 0                  | 0 | indeterminate |   |

| 1                     | 0                  | 1 | 1             | 0 |

| 1                     | 1                  | 0 | 0             | 1 |

| 1                     | 1                  | 1 | 1             | 0 |

| 0                     | 0                  | 0 | indeterminate |   |

| 0                     | 0                  | 1 | 1             | 0 |

| 0                     | 1                  | 0 | 0             | 1 |

| 0                     | 1                  | 1 | 0             | 1 |

or more simply shown in Table 2

Table 2: Simple NAND R-S Flip Flop Truth

#### Table

| s | R | Q             |  |

|---|---|---------------|--|

| 0 | 0 | indeterminate |  |

| 0 | 1 | Set (1)       |  |

| 1 | 0 | Reset(0)      |  |

| 1 | 1 | No Change     |  |

When NOR gate are used the R and S inputs are transposed compared with the NAND version. Also the stable state when R and S are both 0. A change of state is effected by pulsing the appropriate input to the 1 state. The indeterminate state is now when both R and S are simultaneously at logic 1. Table 3 shows this operation.

Table 3: NOR Gate R-S Flip Flop Truth Table

| S | R | Q             |  |  |

|---|---|---------------|--|--|

| 0 | 0 | No Change     |  |  |

| 0 | 1 | Reset (0)     |  |  |

| 1 | 0 | Set (1)       |  |  |

| 1 | 1 | Indeterminate |  |  |

The RS latch flip flop required the direct input but no clock. It is very use full to add clock to control precisely the time at which the flip flop changes the state of its output.

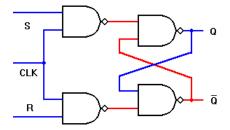

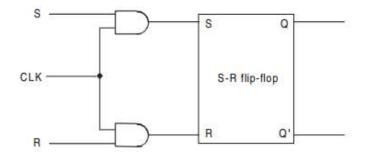

In the clocked R-S flip flop the appropriate levels applied to their inputs are blocked till the receipt of a pulse from an other source called clock. The flip flop changes state only when clock pulse is applied depending upon the inputs. The basic circuit is shown in Figure 2. This circuit is formed by adding two AND gates at inputs to the R-S flip flop. In addition to control inputs Set (S) and Reset (R), there is a clock input (C) also.

Figure 2: Clocked RS Flip Flop

Table 4: The truth table for the Clocked R-S flip flop

| Initial<br>Conditions | Inpu<br>(Pul |   | Final<br>Output | Comment       |

|-----------------------|--------------|---|-----------------|---------------|

| Q                     | s            | R | Q (t + 1)       | No Change     |

| 0                     | 0            | 0 | 0               | No Change     |

| 0                     | 0            | 1 | 0               | Clear Q       |

| 0                     | 1            | 0 | 1               | Set Q         |

| 0                     | 1            | 1 | ???             | indeterminate |

| 1                     | 0            | 0 | 1               | No Change     |

| 1                     | 0            | 1 | 0               | Clear Q       |

| 1                     | 1            | 0 | 1               | Set Q         |

| 1                     | 1            | 1 | ???             | indeterminate |

The excitation table for R-S flip flop is very simply derived as given below

Table 5: Excitation table for R-S Flip Flop

| s | R | Q             |  |

|---|---|---------------|--|

| 0 | 0 | No Change     |  |

| 0 | 1 | Reset (0)     |  |

| 1 | 0 | Set (1)       |  |

| 1 | 1 | Indeterminate |  |

## D Flip Flop

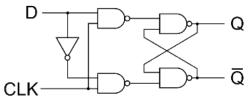

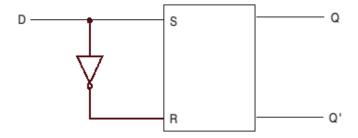

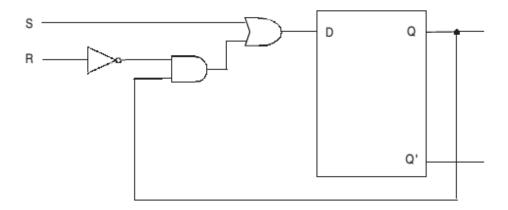

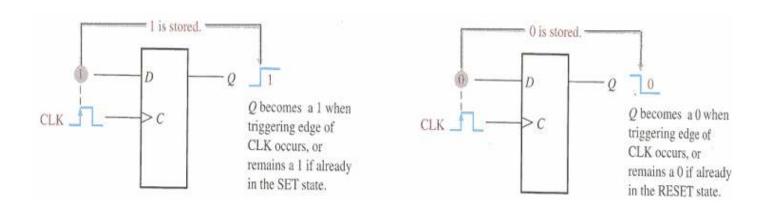

A D type (Data or delay flip flop) has a single data input in addition to the clock input as shown in Figure 3.

Figure 3: D Flip Flop

Basically, such type of flip flop is a modification of clocked RS flip flop gates from a basic Latch flip flop and NOR gates modify it in to a clock RS flip flop. The D input goes directly to S input and its complement through NOT gate, is applied to the R input.

This kind of flip flop prevents the value of D from reaching the output until a clock pulse occurs. The action of circuit is straight forward as follows.

When the clock is low, both AND gates are disabled, there fore D can change values with out affecting the value of Q. On the other hand, when the clock is high, both AND gates are enabled. In this case, Q is forced equal to D when the clock again goes low, Q retains or stores the last value of D. The truth table for such a flip flop is as given below in table 6.

Table 6: Truth table for D

#### Flip Flop

| s | R | Q(t +<br>1) |

|---|---|-------------|

| 0 | 0 | 0           |

| 0 | 1 | 1           |

| 1 | 0 | 0           |

| 1 | 1 | 1           |

The excitation table for D flip flop is very simply derived given as under.

#### Table 7: Excitation

#### table for D Flip

#### Flop

| s | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

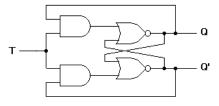

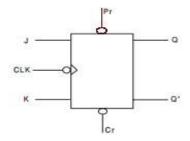

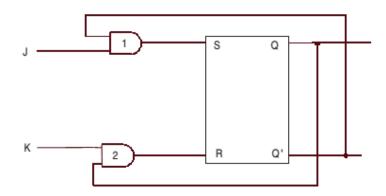

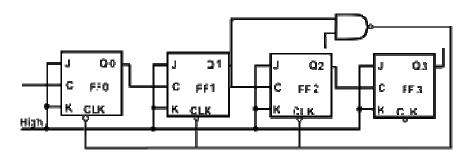

#### JK Flip Flop

One of the most useful and versatile flip flop is the JK flip flop the unique features of a JK flip flop are:

- 1. If the J and K input are both at 1 and the clock pulse is applied, then the output will change state, regardless of its previous condition.

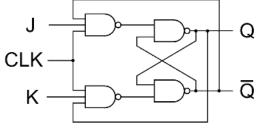

- 2. If both J and K inputs are at 0 and the clock pulse is applied there will be no change in the output. There is no indeterminate condition, in the operation of JK flip flop i.e. it has no ambiguous state. The circuit diagram for a JK flip flop is shown in Figure 4.

Figure 4: JK Flip Flop

#### When J = 0 and K = 0

These J and K inputs disable the NAND gates, therefore clock pulse have no effect on the flip flop. In other words, Q returns it last value.

#### When J = 0 and K = 1,

The upper NAND gate is disabled the lower NAND gate is enabled if Q is 1 therefore, flip flop will be reset (Q = 0,  $\overline{Q}$  =1)if not already in that state.

#### When J = 1 and K = 0

The lower NAND gate is disabled and the upper NAND gate is enabled if  $\overline{Q}$  is at 1, As a result we will be able to set the flip flop ( Q = 1,  $\overline{Q} = 0$ ) if not already set

#### When J = 1 and K = 1

If Q = 0 the lower NAND gate is disabled the upper NAND gate is enabled. This will set the flip flop and hence Q will be 1. On the other hand if Q = 1, the lower NAND gate is enabled and flip flop will be reset and hence Q will be 0. In other words, when J and K are both high, the clock pulses cause the JK flip flop to toggle. Truth table for JK flip flop is shown in table 8.

Table 8: The truth table for the JK flip flop

| Initial<br>Conditions | Inputs<br>(Pulsed) |   | Final<br>Output |

|-----------------------|--------------------|---|-----------------|

| Q                     | s                  | R | Q (t + 1)       |

| 0                     | 0                  | 0 | 0               |

| 0                     | 0                  | 1 | 0               |

| 0                     | 1                  | 0 | 1               |

| 0                     | 1                  | 1 | 1               |

| 1                     | 0                  | 0 | 1               |

| 1                     | 0                  | 1 | 0               |

| 1                     | 1                  | 0 | 1               |

| 1                     | 1                  | 1 | 0               |

The excitation table for JK flip flop is very simply derived as given in table 9.

Table 9: Excitation table for

#### JK Flip Flop

| s | R | Q            |

|---|---|--------------|

| 0 | 0 | No<br>Change |

| 0 | 1 | 0            |

| 1 | 0 | 1            |

| 1 | 1 | Toggle       |

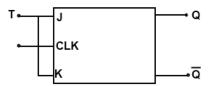

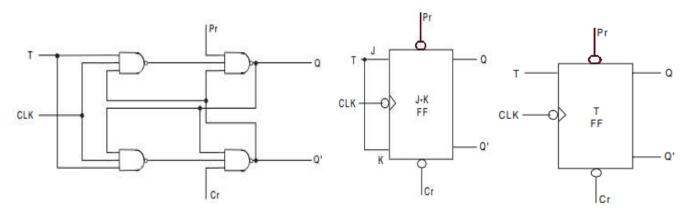

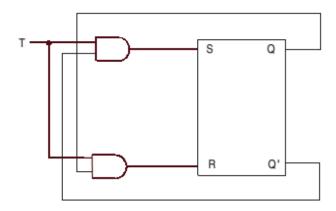

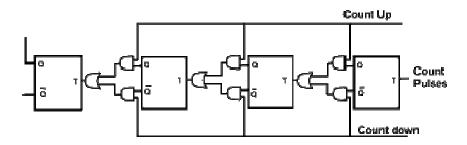

### T Flip Flop

A method of avoiding the indeterminate state found in the working of RS flip flop is to provide only one input ( the T input ) such, flip flop acts as a toggle switch. Toggle means to change in the previous stage i.e. switch to opposite state. It can be constructed from clocked RS flip flop be incorporating feedback from output to input as shown in Figure 5.

Figure 5: T Flip Flop

Such a flip flop is also called toggle flip flop. In such a flip flop a train of extremely narrow triggers drives the T input each time one of these triggers, the output of the flip flop changes stage. For instance Q equals 0 just before the trigger. Then the upper AND gate is enable and the lower AND gate is disabled. When the trigger arrives, it results in a high S input.

This sets the Q output to 1. When the next trigger appears at the point T, the lower AND gate is enabled and the trigger passes through to the R input this forces the flip flop to reset.

Since each incoming trigger is alternately changed into the set and reset inputs the flip flop toggles. It takes two triggers to produce one cycle of the output waveform. This means the output has half the frequency of the input stated another way, a T flip flop divides the input frequency by two. Thus such a circuit is also called a divide by two circuit.

A disadvantage of the toggle flip flop is that the state of the flip flop after a trigger pulse has been applied is only known if the previous state is known. The truth table for a T flip flop is as given table 7.

Table 7: Truth table for T

#### Flip Flop

| Q <sub>n</sub> | Т | Q <sub>n</sub> + 1 |

|----------------|---|--------------------|

| 0              | 0 | 0                  |

| 0              | 1 | 1                  |

| 1              | 0 | 1                  |

| 1              | 1 | 0                  |

The excitation table for T flip flop is very simply derived as shown in Table 8.

Table 8: Excitation table for T Flip Flop

| Т | Q                |

|---|------------------|

| 0 | Q <sub>n</sub>   |

| 1 | $\overline{Q}_n$ |

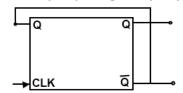

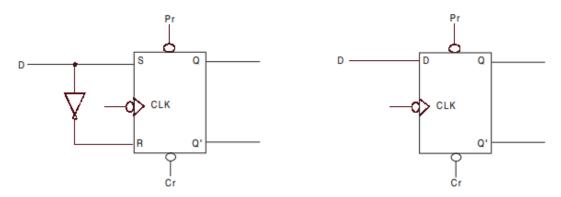

Generally T flip flop ICs are not available. It can be constructed using JK, RS or D flip flop. Figure 6 shows the relation of T flip flop using JK flip flop.

Figure 6: T Flip Flop Using JK Flip Flop

Figure 7: D-type Flip Flop connected as toggle stage

Figure 7: JK & D Flip Flop Connected as T Flip flop

A D-type flip flop may be modified by external connection as a T-type stage as shown in Figure 7. Since the Q logic is used as D-input the opposite of the Q output is transferred into the stage each clock pulse. Thus the stage having Q - 0 transistors  $\overline{Q}$ = 1, Providing a toggle action, if the stage had Q = 1 the clock pulse would result in Q = 0 being transferred, again providing the toggle operation. The D-type flip flop connected as in Figure 6 will thus operate as a T-type stage, complementing each clock pulse.

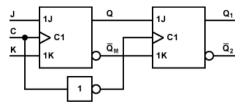

# Master Slave Flip Flop

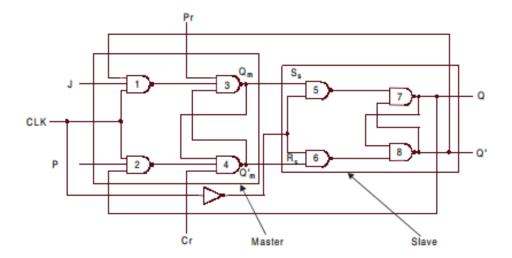

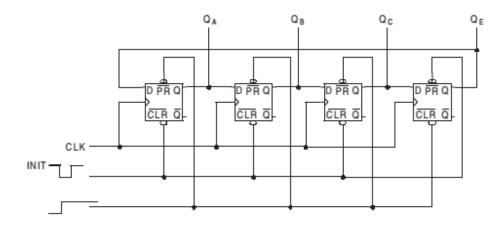

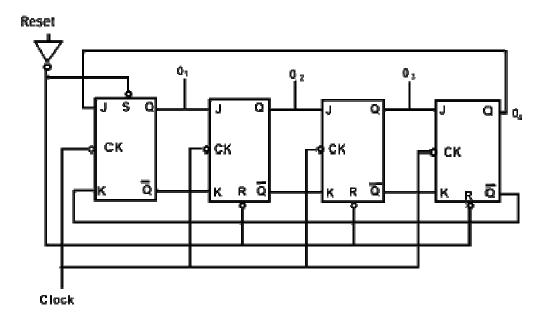

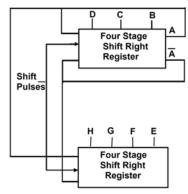

Figure 8 shows the schematic diagram of master sloave J-K flip flop

Figure 8: Master Slave JK Flip Flop

#### Figure 8: Master Slave JK Flip Flop

A master slave flip flop contains two clocked flip flops. The first is called master and the second slave. When the clock is high the master is active. The output of the master is set or reset according to the state of the input. As the slave is incative during this period its output remains in the previous state. When clock becomes low the output of the slave flip flop changes because it become active during low clock period. The final output of master slave flip flop is the output of the slave flip flop. So the output of master slave flip flop is available at the end of a clock pulse.

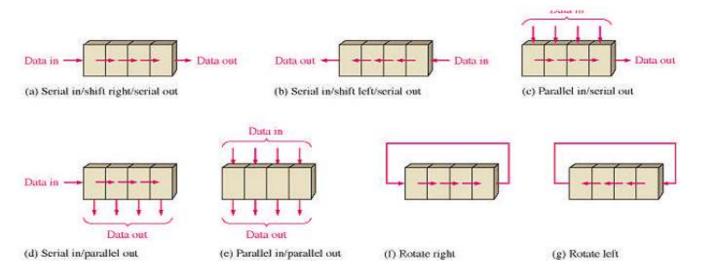

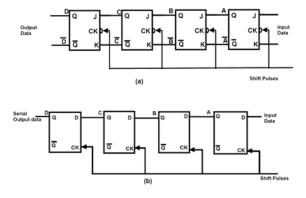

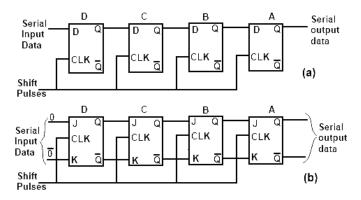

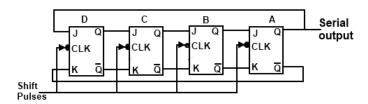

- Clocked or Triggered Flip Flops

- Shift Registers

- Applications of Flip Flops

Category: <u>Digital Electronics</u>

< <u>Digital To Analog Converter (DAC)</u>

<u>Up</u>

Instruction Set of Intel 8085 Microprocessor >

Privacy & Disclaimer Terms of Service Sitemap

# **Module-3**

# SEQUENTIAL LOGIC CIRCUITS

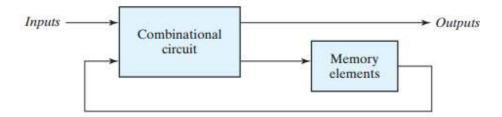

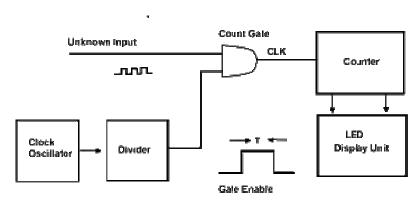

Till now we studied the logic circuits whose outputs at any instant of time depend only on the input signals present at that time are known as combinational circuits. Moreover, in a combinational circuit, the output appears immediately for a change in input, except for the propagation delay through circuit gates.

On the other hand, the logic circuits whose outputs at any instant of time depend on the present inputs as well as on the past outputs are called sequential circuits. In sequential circuits, the output signals are fed back to the input side. A block diagram of a sequential circuit is shown in Figure below:-

It consists of a combinational circuit to which storage elements are connected to form a feedback path. The storage elements are devices capable of storing binary information. The binary information stored in these elements at any given time defines the *state* of the sequential circuit at that time. The sequential circuit receives binary information from external inputs that, together with the present state of the storage elements, determine the binary value of the outputs. These external inputs also determine the condition for changing the state in the storage elements. The block diagram demonstrates that the outputs in a sequential circuit are a function not only of the inputs, but also of the present state of the storage elements. The next state of the storage elements is also a function of external inputs and the present state. Thus, a sequential circuit is specified by a time sequence of inputs, outputs, and internal states.

There are two types of sequential circuits, and their classification is a function of the timing of their signals.

#### Asynchronous sequential circuit:

A sequential circuit whose behavior depends upon the sequence in which the input signals change is referred to as an *asynchronous sequential circuit*. The output will be affected whenever the input changes. The commonly used memory elements in these circuits are time-delay devices. There is no need to wait for a clock pulse. Therefore, in general, asynchronous circuits are faster than synchronous sequential circuits. However, in an asynchronous circuit, events are allowed to occur without any synchronization. And in such a case, the system becomes unstable. Since the designs of asynchronous circuits are more tedious and difficult, their uses are rather limited. The memory elements used in sequential circuits are flip-flops which are capable of storing binary information.

#### Synchronous sequential circuit:

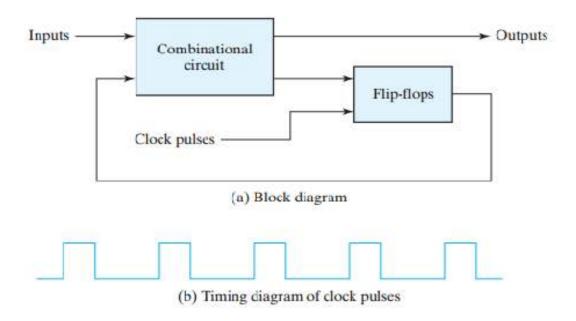

A sequential circuit whose behavior can be defined from the knowledge of its signal at discrete instants of time is referred to as a *synchronous sequential circuit*. In these systems, the memory elements are affected only at discrete instants of time. The synchronization is achieved by a timing device known as a system clock, which generates a periodic train of lock pulses. The outputs are affected only with the application of a clock pulse.

Synchronous clocked sequential circuit

The storage elements (memory) used in clocked sequential circuits are called *flipflops*

### **FLIPFLOPS**

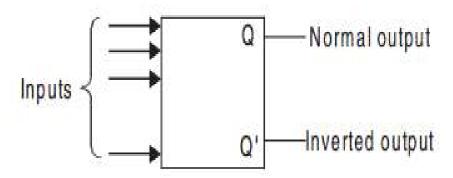

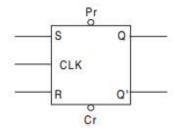

The basic 1-bit digital memory circuit is known as a flip-flop. It can have only two states, either the 1 state or the 0 state. A flip-flop is also known as a bistable multivibrator. Flip-flops can be obtained by using NAND or NOR gates. The general block diagram representation of a flip-flop is shown in Figure below. It has one or more inputs and two outputs. The two outputs are complementary to each other. If Q is 1 *i.e.*, Set, then Q' is 0; if Q is 0 *i.e.*, Reset, then Q' is 1. That means Q and Q' cannot be at the same state simultaneously. If it happens by any chance, it violates the definition of a flip-flop and hence is called an *undefined* condition. Normally, the state of Q is called the *state* of the flip-flop, whereas the state of Q' is called the *complementary state* of the flip-flop. When the output Q is either 1 or 0, it remains in that state unless one or more inputs are excited to effect a change in the output. Since the output of the flip-flop remains in the same state until the trigger pulse is applied to change the state, it can be regarded as a memory device to store one binary bit. The block diagram of a flip-flop is given below:-

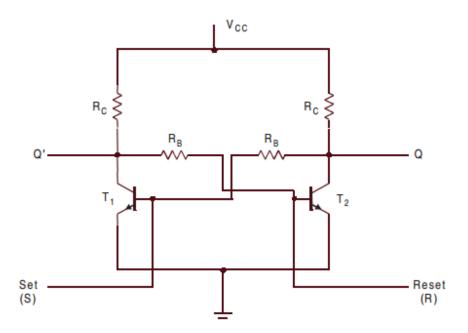

The Bistable multivibrator circuit of a flip-flop is given below:-

From the circuit shown in above, the multivibrator is basically two cross-coupled inverting amplifiers, consist of two transistors and four resistors. Obviously, if transistor  $T_1$  is initially turned ON (saturated) by applying a positive signal through the Set input at its base, its collector will be at  $V_{CE(sat)}$  (0.2 to 0.4 V). The collector of  $T_1$  is connected to the base of  $T_2$ , which cannot turn  $T_2$  On. Hence,  $T_2$  remains OFF (cut off). Therefore, the voltage at the collector of  $T_2$  tries to reach  $V_{CC}$ . This action only enhances the initial positive signal applied to the base of  $T_1$ . Now if the initial signal at the Set input is removed, the circuit will maintain  $T_1$  in the ON state and  $T_2$  in the OFF state indefinitely, *i.e.*, Q = 1 & Q' = 0. In this condition the bistable multivibrator is said to be in the **Set state**. A positive signal applied to the Reset input at the base of  $T_2$  turns it ON. As we have discussed earlier, in the same sequence  $T_2$  turns ON &  $T_1$  turns OFF, resulting in a second stable state *i.e.* Q = 0 & Q' = 1. In this condition the bistable multivibrator is said to be in the *Reset* state.

# **LATCHES**

The basic difference between a latch & flip-flop is, Storage elements that operate with signal levels (rather than signal transitions) are referred to as **latches**; those controlled by a clock transition are **flip-flops**. Latches are said to be level sensitive devices; flip-flops are edge-sensitive devices.

The two types of storage elements are related because latches are the basic circuits from which all flip-flops are constructed.

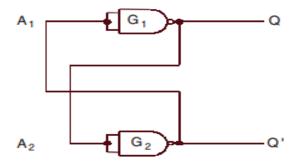

We consider the fundamental circuit shown in Fig.(last page). It consists of two inverters  $G_1$  and  $G_2$  (NAND gates are used as inverters). The output of  $G_1$  is connected to the input of  $G_2$  (A<sub>2</sub>) and the output of  $G_2$  is connected to the input of  $G_1$  (A<sub>1</sub>).

Let us assume the output of  $G_1$  to be Q = 0, which is also the input of  $G_2$  ( $A_2 = 0$ ). So, the output of  $G_2$  will be Q' = 1, which makes  $A_1 = 1$  and consequently Q = 0 which is according to our assumption. Similarly, we can demonstrate that if Q = 1, then Q' = 0 and this is also consistent with the circuit connections. Hence we see that Q and Q' are always complementary. And if the circuit is in 1 state, it continues to remain in this state and vice versa is also true. Since this information is locked or latched in this circuit, therefore, this circuit is also referred to as a *latch*. In this circuit there is no way to enter the desired digital information to be stored in it. To make that possible we have to modify the circuit by replacing the inverters by NAND gates and then it becomes a flip-flop.

### **TYPES OF FLIP-FLOPS**

There are different types of flip-flops depending on how their inputs and clock pulses cause transition between two states. We will discuss four different types of flip-flops in this chapter, *viz.*, S-R, D, J-K, and T. Basically D, J-K, and T are three different modifications of the S-R flip-flop.

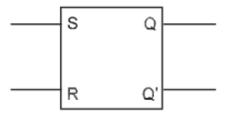

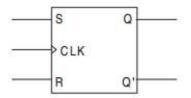

#### S-R (Set-Reset) Flip-flop

An S-R flip-flop has two inputs named Set (S) and Reset (R), and two outputs Q and Q'. The outputs are complement of each other, *i.e.*, if one of the outputs is 0 then the other should be 1. This can be implemented using NAND or NOR gates. The block diagram of an S-R flip-flop is shown in Figure below:-

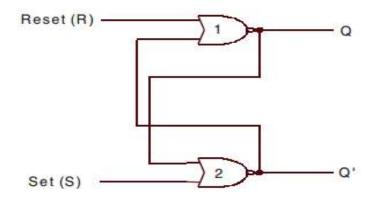

### S-R Flip-flop Based on NOR Gates

An S-R flip-flop can be constructed with NOR gates at ease by connecting the NOR gates back to back as shown in Figure below. The cross-coupled connections from the output of gate 1 to the input of gate 2 constitute a feedback path. This circuit is not clocked and is classified as an asynchronous sequential circuit. The truth table for the S-R flip-flop based on a NOR gate is shown in the table below

| Inp | outs | Outp      | outs       | Action                |  |

|-----|------|-----------|------------|-----------------------|--|

| s   | R    | $Q_{n+1}$ | $Q'_{n+1}$ |                       |  |

| 0   | 0    | $Q_n$     | Q'a        | No change             |  |

| 0   | 1    | 0         | 1          | Reset                 |  |

| 1   | 0    | 1         | 0          | Set                   |  |

| 1   | 1    | 0         | 0          | Forbidden (Undefined) |  |

| 0   | 0    | _         | _          | Indeterminate         |  |

To analyze the circuit of S-R Flip-flop Based on NOR Gates, we have to consider the fact that the output of a NOR gate is 0 if any of the inputs are 1, irrespective of the other input. The output is 1 only if all of the inputs are 0. The outputs for all the possible conditions as shown in the above table are described as follows.

Case 1. For S = 0 and R = 0, the flip-flop remains in its present state  $(Q_n)$ . It means that the next state of the flip-flop does not change, *i.e.*,  $Q_{n+1} = 0$  if  $Q_n = 0$  and vice versa. First let us assume that  $Q_n = 1$  and  $Q'_n = 0$ . Thus the inputs of NOR gate 2 are 1 and 0, and therefore its output  $Q'_n + 1 = 0$ . This output  $Q'_{n+1} = 0$  is fed back as the input of NOR gate 1, thereby producing a 1 at the output, as both of the inputs of NOR gate 1 are 0 and 0; so  $Q_{n+1} = 1$  as originally assumed. Now let us assume the opposite case, *i.e.*,  $Q_n = 0$  and  $Q'_n = 1$ . Thus the inputs of NOR gate 1 are 1 and 0, and therefore its output  $Q'_{n+1} = 0$ . This output  $Q_{n+1} = 0 = 0$  is fed back as the input of NOR gate 2, thereby producing a 1 at the output, as both of the inputs of NOR gate 2 are 0 and 0; so  $Q'_{n+1} = 1$  as originally assumed. Thus we find that the condition S = 0 and R = 0 do not affect the outputs of the flip-flop, which means this is the memory condition of the S-R flip-flop.

Case 2. The second input condition is S = 0 and R = 1. The 1 at R input forces the output of NOR gate 1 to be 0 (*i.e.*,  $Q_{n+1} = 0$ ). Hence both the inputs of NOR gate 2 are 0 and 0 and so its output  $Q'_{n+1} = 1$ . Thus the condition S = 0 and R = 1 will always reset the flip-flop to 0. Now if the R returns to 0 with S = 0, the flip-flop will remain in the same state.

Case 3. The third input condition is S = 1 and R = 0. The 1 at S input forces the output of NOR gate 2 to be 0 (*i.e.*,  $Q'_{n+1} = 0$ ). Hence both the inputs of NOR gate 1 are 0 and 0 and so its output  $Q_{n+1} = 1$ . Thus the condition S = 1 and R = 0 will always set the flip-flop to 1. Now if the S returns to 0 with R = 0, the flip-flop will remain in the same state.

Case 4. The fourth input condition is S = 1 and R = 1. The 1 at R input and 1 at S input forces the output of both NOR gate 1 and NOR gate 2 to be 0. Hence both the outputs of NOR gate 1 and NOR gate 2 are 0 and 0; *i.e.*,  $Q_{n+1} = 0$  and  $Q'_{n+1} = 0$ . Hence this condition S = 1 and R = 1 violates the fact that the outputs of a flip-flop will always be the complement of each other. Since the condition violates the basic definition of flip-flop, it is called the *undefined* condition. Generally this condition must be avoided by making sure that 1s are not applied simultaneously to both of the inputs.

Case 5. If case 4 arises at all, then S and R both return to 0 and 0 simultaneously, and then any one of the NOR gates acts faster than the other and assumes the state. For example, if NOR gate 1 is faster than NOR gate 2,

then  $Q_{n+1}$  will become 1 and this will make  $Q'_{n+1} = 0$ . Similarly, if NOR gate 2 is faster than NOR gate 1, then  $Q'_{n+1}$  will become 1 and this will make  $Q_{n+1} = 0$ . Hence, this condition is determined by the flip-flop itself. Since this condition cannot be controlled and predicted it is called the *indeterminate* condition.

Similarly we can analyze the case of S'-R' Flip-flop Based on NAND Gates (assignment for the students).

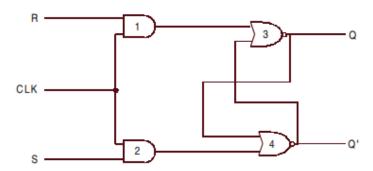

### **CLOCKED S-R FLIP-FLOP**

Generally, synchronous circuits change their states only when clock pulses are present. The operation of the basic flip-flop can be modified by including an additional input to control the behavior of the circuit. Such a circuit is shown below:-

The circuit shown above consists of two AND gates. The clock input is connected to both of the AND gates, resulting in LOW outputs when the clock input is LOW. In this situation the changes in S and R inputs will not affect the state (Q) of the flip-flop. On the other hand, if the clock input is HIGH, the changes in S and R will be passed over by the AND gates and they will cause changes in the output (Q) of the flip-flop. This way, any information, either 1 or 0, can be stored in the flip-flop by applying a HIGH clock input and be retained for any desired period of time by applying a LOW at the clock input. This type of flip-flop is called a *clocked S-R flip-flop*. Such a clocked S-R flip-flop made up of two AND gates and two NOR gates is shown in Figure below:-

The logic symbol of the S-R flip-flop is shown below. It has three inputs: S, R, and CLK. The CLK input is marked with a small triangle. The triangle is a symbol that denotes the fact that the circuit responds to an edge or transition at CLK input.

Assuming that the inputs do not change during the presence of the clock pulse, we can express the working of the S-R flip-flop in the form of the truth table shown here. Here,  $S_n$  and  $R_n$  denote the inputs and  $Q_n$  denotes the output during the bit time n.  $Q_{n+1}$  denotes the output after the pulse passes *i.e.* in the bit time n + 1.

| Inj   | puts    | Output    |

|-------|---------|-----------|

| $S_n$ | $R_{n}$ | $Q_{n+1}$ |

| 0     | 0       | $Q_n$     |

| 0     | 1       | 0         |

| 1     | 0       | 1         |

| 1     | 1       | _         |

Case 1. If  $S_n = R_n = 0$ , and the clock pulse is not applied, the output of the fl ip-fl op remains in the present state. Even if  $S_n = R_n = 0$ , and the clock pulse is applied, the output at the end of the clock pulse is the same as the output before the clock pulse, i.e.,  $Q_{n+1} = Q_n$ . The first row of the table indicates that situation. Case 2. For  $S_n = 0$  and  $R_n = 1$ , if the clock pulse is applied (i.e. CLK = 1), the output of NAND gate 1 becomes 1; whereas the output of NAND gate 2 will be 0. Now a 0 at the input of NAND gate 4 forces the output to be 1 i.e. Q' = 1. This 1 goes to the input of NAND gate 3 to make both the inputs of NAND gate 3 as 1, which forces the output of **NAND** to be 0, i.e., gate 0 Case 3. For  $S_n = 1$  and  $R_n = 0$ , if the clock pulse is applied (i.e., CLK = 1), the output of NAND gate 2 becomes 1; whereas the output of NAND gate 1 will be 0. Now a 0 at the input of NAND gate 3 forces the output to be 1, i.e., Q = 1. This 1 goes to the input of NAND gate 4 to make both the inputs of NAND gate 4 as 1, which forces of **NAND** be gate to 0. Case 4. For  $S_n = 1$  and  $R_n = 1$ , if the clock pulse is applied (i.e. CLK = 1), the outputs of both NAND gate 2 and NAND gate 1 becomes 0. Now a 0 at the input of both NAND gate 3 and NAND gate 4 forces the outputs of both the gates to be 1, i.e., Q = 1 and Q' = 1. When the CLK input goes back to 0 (while S and R remain at 1), it is not possible to determine the next state, as it depends on whether the output of gate 1 or gate 2 goes to 1 first.

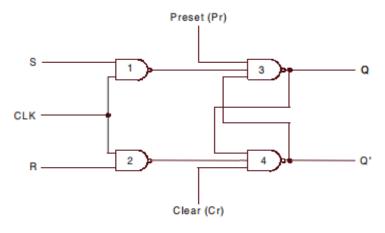

### **Preset and Clear**

Till now the flip-flops we discussed there when the power is switched on, the state of the circuit is uncertain. It may come to reset (Q = 0) or set (Q = 1) state. But in many applications it is required to initially set or reset the flip-flop, *i.e.*, the initial state of the flip-flop is to be assigned. This is done by using the direct or asynchronous inputs. These inputs are referred to as *preset* (**Pr**) and *clear* (**Cr**) inputs. These inputs may be applied at any time between clock pulses and is not in synchronism with the clock. Such an S-R flip-flop containing preset and clear inputs is shown in Figure below.

From the above Figure, we see that if Pr = Cr = 1, the circuit operates according to the table of clocked S-R flip-flop as we discussed just before.

If Pr = 1 and Cr = 0, the output of NAND gate 4 is forced to be 1, *i.e.*, Q' = 1 and the flip-flop is reset, overwriting the previous state of the flip-flop.

If Pr = 0 and Cr = 1, the output of NAND gate 3 is forced to be 1, *i.e.*, Q = 1 and the flip-flop is set, overwriting the previous state of the flip-flop. Once the state of the flip-flop is established asynchronously, the inputs Pr and Pr must be connected to logic 1 before the next clock is applied.

The condition Pr = Cr = 0 must not be applied, since this leads to an uncertain state.

The logic symbol of an S-R flip-flop with Pr and Cr inputs is shown in the side. Here, bubbles are used for Pr and Cr inputs, which indicate these are active low inputs, which means that the intended function is performed if the signal applied to Pr and Cr is LOW. The operation of the clocked S-R flip-flop is shown in the table in below. The circuit can be designed such that the asynchronous inputs override the clock, *i.e.*, the circuit can be set or reset even in the presence of the clock pulse.

|     | Inputs | 0  | Output                 | Operation        |

|-----|--------|----|------------------------|------------------|

| CLK | Cr     | Pr | Q                      | performed        |

| 1   | 1      | 1  | $Q_{n+1}$ (Figure 7.3) | Normal flip-flop |

| 0   | 1      | 0  | 1                      | Preset           |

| 0   | 0      | 1  | 0                      | Clear            |

| 0   | 0      | 0  | = :                    | Uncertain        |

## **Characteristic Table of an S-R Flip-flop**

From the name itself it is very clear that the *characteristic table* of a flip-flop actually gives us an idea about the character, *i.e.*, the working of the flip-flop. Now, from all our above discussions, we know that the next state flip-flop output  $(Q_{n+1})$  depends on the present inputs as well as the present output  $(Q_n)$ . So in order to know the next state output of a flip-flop, we have to consider the present state output also. The characteristic table of an S-R fl ip-fl op is given in the table below. From the characteristic table we have to find out the characteristic equation of the S-R flip-flop.

| Flip-fle | p inputs | Present output | Next output |

|----------|----------|----------------|-------------|

| s        | R        | $Q_n$          | $Q_{n+1}$   |

| 0        | 0        | 0              | 0           |

| 0        | 0        | 1              | 1           |

| 0        | 1        | 0              | 0           |

| 0        | 1        | 1              | 0           |

| 1        | 0        | 0              | 1           |

| 1        | 0        | 1              | 1           |

| 1        | 1        | 0              | X           |

| 1        | 1        | 1              | X           |

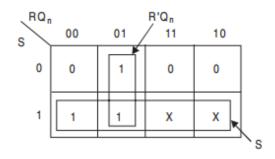

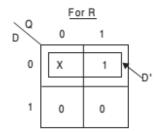

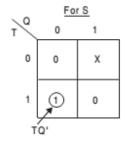

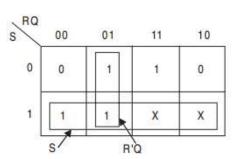

Now we will find out the characteristic equation of the S-R flip-flop from the characteristic table with the help of the Karnaugh map:-

From the Karnaugh map above we find the expression for  $Q_{n+1}$  as

$$Q_{n+1} = S + R'Q_n$$

Along with the above equation we have to consider the fact that S and R cannot be simultaneously 0. In order to take that fact into account we have to incorporate another equation for the S-R flip-flop. The equation is given below.

Hence the characteristic equations of an S-R flip-flop are

$$Q_{n+1} = S + R' Q_n$$

$$SR = 0$$

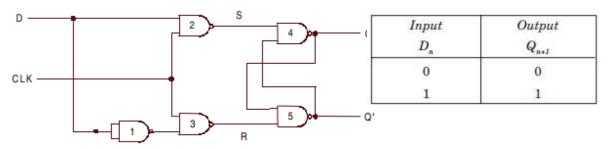

### **CLOCKED D FLIP-FLOP**

One way to eliminate the undesirable condition of the indeterminate state in the SR latch is to ensure that inputs S and R are never equal to 1 at the same time. This is done in the D latch. The D flip-flop has only one input referred to as the D (data) input & two outputs as usual Q and Q'. It transfers the data at the input after the delay of one clock pulse at the output Q. So in some cases the input is referred to as a delay input and the flip-flop gets the name delay (D) flip-flop. It can be easily constructed from an S-R flip-flop by simply incorporating an inverter between S and R such that the input of the inverter is at the S end & the output of the inverter is at the R end. We can get rid of the undefined condition, i.e., S = R = 1 condition, of the S-R flip-flop in the D flip flop. The D flip-flop is either used as a delay device or as a latch to store one bit of binary information. The truth table of D flip-flop is given in the table below. The structure of the D flip-flop is shown in Figure below, which is being constructed using NAND gates. The same structure can be constructed using only NOR gates.

**Case 1.** If the CLK input is low, the value of the D input has no effect, since the S and R inputs of the basic NAND flip-flop are kept as 1.

Case 2. If the CLK = 1 and D = 1, the NAND gate 1 produces 0, which forces the output of NAND gate 3 as 1. On the other hand, both the inputs of NAND gate 2 are 1, which gives the output of gate 2 as 0. Hence, output

of NAND gate 4 is forced to be 1, *i.e.*, Q = 1, whereas both the inputs of gate 5 are 1 and the output is 0, *i.e.*, Q' = 0. Hence, we find that when D = 1, after one clock pulse passes Q = 1, which means the output follows D. **Case 3.** If the CLK = 1, and D = 0, the NAND gate 1 produces 1. Hence both the inputs of NAND gate 3 are 1, which gives the output of gate 3 as 0. On the other hand, D = 0 forces the output of NAND gate 2 to be 1. Hence the output of NAND gate 5 is forced to be 1, *i.e.*, Q' = 1, whereas both the inputs of gate 4 are 1 and the output is 0, *i.e.*, Q = 0. Hence, we find that when D = 0, after one clock pulse passes Q = 0, which means the output again follows D.

A simple way to construct a D flip-flop using an S-R flip-flop is shown in Figure below. The logic symbol of a D flip-flop is shown in Figure below. A D flip-flop is most often used in the construction of sequential circuits like registers.

### Characteristic Table of a D Flip-flop

As we have already discussed the characteristic equation of an S-R flip-flop, we can similarly find out the characteristic equation of a D flip-flop. The characteristic table of a D flip-flop is given in the table below. From the characteristic table we have to find out the characteristic equation of the D flip-flop.

| Flip-flop inputs | Present output | Next output  |

|------------------|----------------|--------------|

| D                | $Q_{n}$        | $Q_{_{n+1}}$ |

| 0                | 0              | 0            |

| 0                | 1              | 0            |

| 1                | 0              | 1            |

| 1                | 1              | 1            |

Now we will find out the characteristic equation of the D flip-flop from the characteristic table with the help of the Karnaugh map:-

Hence, the characteristic equation of a D flip-flop is

$\mathbf{Q}_{n+1} = \mathbf{D}$

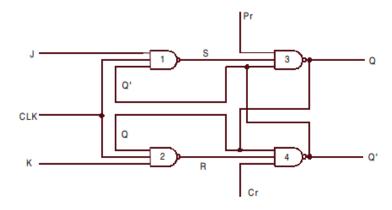

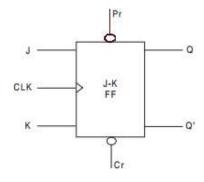

### J-K FLIP-FLOP

A J-K flip-flop has very similar characteristics to an S-R flip-flop. The only difference is that the undefined condition for an S-R flip-flop, *i.e.*,  $S_n = R_n = 1$  condition, is also included in this case. Inputs J and K behave like inputs S and R to set and reset the flip-flop respectively. When J = K = 1, the flip-flop is said to be in a *toggle state*, which means the output switches to its complementary state every time a clock passes.

The data inputs are J and K, which are ANDed with Q' and Q respectively to obtain the inputs for S and R respectively. A J-K flip-flop thus obtained is shown in Figure below.

An S-R flip-flop converted into a J-K flip-flop:-

A J-K flip-flop using NAND gates:-

Logic symbol of a J-K flip-flop:-

The TRUTH table for JK flip-flop is:-

| Data  | inputs | Out   | puts   | Inputs to | S-R FF                        | Output    |

|-------|--------|-------|--------|-----------|-------------------------------|-----------|

| $J_n$ | $K_n$  | $Q_n$ | $Q'_n$ | $S_n$     | $R_{_{\scriptscriptstyle R}}$ | $Q_{n+1}$ |

| 0     | 0      | 0     | 1      | 0         | 0                             | 0         |

| 0     | 0      | 1     | 0      | 0         | 0                             | 1         |

| 0     | 1      | 0     | 1      | 0         | 0                             | 0         |

| 0     | 1      | 1     | 0      | 0         | 1                             | 0         |

| 1     | 0      | 0     | 1      | 1         | 0                             | 1         |

| 1     | 0      | 1     | 0      | 0         | 0                             | 1         |

| 1     | 1      | 0     | 1      | 1         | 0                             | 1         |

| 1     | 1      | 1     | 0      | 0         | 1                             | 0         |

| Inp     | outs    | Output         |

|---------|---------|----------------|

| $J_{n}$ | $K_{n}$ | $Q_{n+1}$      |

| 0       | 0       | Q <sub>n</sub> |

| 0       | 1       | 0              |

| 1       | 0       | 1              |

| 1       | 1       | Q'n            |

Case 1. When the clock is applied and J = 0, whatever the value of  $Q'_n$  (0 or 1), the output of NAND gate 1 is 1. Similarly, when K = 0, whatever the value of  $Q_n$  (0 or 1), the output of gate 2 is also 1. Therefore, when J = 0 and K = 0, the inputs to the basic flip-flop are S = 1 and R = 1. This condition forces the flip-flop to remain in the same state.

Case 2. When the clock is applied and J = 0 and K = 1 & the previous state of the flip-flop is reset (*i.e.*,  $Q_n = 0$  and  $Q'_n = 1$ ), then S = 1 and R = 1. Since S = 1 and R = 1, the basic flip-flop does not alter the state and remains in the reset state. But if the flip-flop is in set condition (*i.e.*,  $Q_n = 1$  &  $Q'_n = 0$ ), then S = 1 and R = 0. Since S = 1 and R = 0, the basic flip-flop changes its state and resets.

Case 3. When the clock is applied and J = 1 and K = 0 and the previous state of the flip-flop is reset (*i.e.*,  $Q_n = 0$  and  $Q'_n = 1$ ), then S = 0 and R = 1. Since S = 0 and R = 1, the basic flip-flop changes its state and goes to the set state. But if the flip-flop is already in set condition (*i.e.*,  $Q_n = 1$  and  $Q'_n = 0$ ), then S = 1 and R = 1. Since S = 1 and R = 1, the basic flip-flop does not alter its state and remains in the set state.

Case 4. When the clock is applied and J = 1 and K = 1 and the previous state of the flip-flop is reset (*i.e.*,  $Q_n = 0$  and  $Q'_n = 1$ ), then S = 0 and R = 1. Since S = 0 and R = 1, the basic flip-flop changes its state and goes to the set state. But if the flip-flop is already in set condition (*i.e.*,  $Q_n = 1$  and  $Q'_n = 0$ ), then S = 1 and R = 0. Since S = 1 and R = 0, the basic flip-flop changes its state and goes to the reset state. So we find that for J = 1 and K = 1, the flip-flop toggles its state from *set* to *reset* and vice versa. Toggle means to switch to the opposite state.

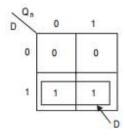

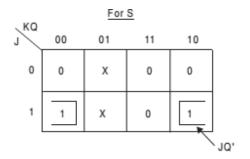

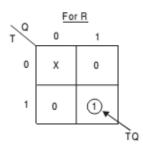

### Characteristic Table of a J-K Flip-flop

As we have already discussed the characteristic equation of an S-R flip-flop, we can similarly find out the characteristic equation of a J-K flip-flop. The characteristic table of a J-K flip-flop is given in the table below. From the characteristic table we have to find out the characteristic equation of the J-K flip-flop.

|  | Flip-flo | p inputs | Present output | Next output |   |     |    |      |                  |      |

|--|----------|----------|----------------|-------------|---|-----|----|------|------------------|------|

|  | J        | K        | $Q_n$          | $Q_{n+1}$   |   |     |    |      |                  |      |

|  | 0        | 0        | 0              | 0           |   |     |    |      |                  |      |

|  | 0        | 0        | 1              | 1           |   |     |    |      |                  |      |

|  | 0        | 1        | 0              | 0           |   |     |    |      |                  |      |

|  | 0        | 1        | 1              | 0           |   | KQ, | 00 | 01 / | K'Q <sub>n</sub> | 10   |

|  | 1        | 0        | 0              | 1           | ' | آ ، |    |      |                  |      |

|  | 1        | 0        | 1              | 1           |   | 0   | 0  |      | 0                | 0    |

|  | 1        | 1        | 0              | 1           |   | 1   | 1  | ,    | 0                | 1    |

|  | 1        | 1        | 1              | 0           |   | l   |    |      |                  | ]O," |

From the Karnaugh map, we obtain  $Q_{n+1} = JQ'_n + K'Q_n$ . Hence, the characteristic equation of a J-K flip-flop is

$$\mathbf{Q}_{n+1} = \mathbf{J}\mathbf{Q'}_n + \mathbf{K'}\mathbf{Q}_n$$

## Race-around Condition of a J-K Flip-flop

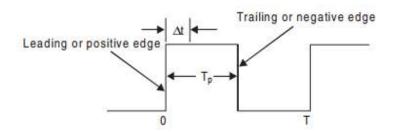

The inherent difficulty of an S-R flip-flop (*i.e.*, S = R = 1) is eliminated by using the feedback connections from the outputs to the inputs of gate 1 and gate 2 as discussed in JK flip-flop. Truth tables JK flip-flop were formed with the assumption that the inputs do not change during the clock pulse (CLK = 1). But the consideration is not true because of the feedback connections. Consider, for example, that the inputs are J = K = 1 and Q = 1, and a pulse as shown in Figure below is applied at the clock input.

Consider, for example, that the inputs are J = K = 1 and Q = 1, and a pulse as shown above is applied at the clock input. After a time interval  $\Delta t$  equal to the propagation delay through two NAND gates in series, the outputs will change to Q = 0. So now we have J = K = 1 and Q = 0. After another time interval of  $\Delta t$  the output will change back to Q = 1. Hence, we conclude that for the time duration of  $t_p$  of the clock pulse, the output will oscillate between 0 and 1. Hence, at the end of the clock pulse, the value of the output is not certain. This situation is referred to as a *race-around condition*.

Generally, the propagation delay of TTL gates is of the order of nanoseconds. So if the clock pulse is of the order of microseconds, then the output will change thousands of times within the clock pulse. This race-around condition can be avoided if  $t_p < \Delta t < T$ . Due to the small propagation delay of the ICs it may be difficult to satisfy the above condition. A more practical way to avoid the problem is to use the master-slave (M-S) configuration as discussed below.

### **Master-Slave J-K Flip-flop**

A master-slave (M-S) flip-flop is shown in Figure below. Basically, a master-slave flip-flop is a system of two flip-flops—one being designated as *master* and the other is the *slave*. From the figure below we see that a clock pulse is applied to the master and the inverted form of the same clock pulse is applied to the slave.

When CLK = 1, the first flip-flop (*i.e.*, the master) is enabled and the outputs  $Q_m$  and  $Q'_m$  respond to the inputs J and K according to the table shown in Figure 7.13. At this time the second flip-flop (*i.e.*, the slave) is disabled because the CLK is LOW to the second flip-flop. Similarly, when CLK becomes LOW, the master becomes disabled and the slave becomes active, since now the CLK to it is HIGH. Therefore, the outputs Q and Q' follow the outputs  $Q_m$  and  $Q'_m$  respectively. Since the second flip-flop just follows the first one, it is referred to as a slave and the first one is called the master. Hence, the configuration is referred to as a master-slave (M-S) flip-flop.

In this type of circuit configuration the inputs to the gates 5 and 6 do not change at the time of application of the clock pulse. Hence the race-around condition does not exist. The state of the master-slave flip-flop, shown in above Figure, changes at the negative transition (trailing edge) of the clock pulse. Hence, it becomes negative triggering a master-slave flip-flop. This can be changed to a positive edge triggering flip-flop by adding two inverters to the system—one before the clock pulse is applied to the master and an additional one in between the master and the slave. The logic symbol of a negative edge master-slave is shown in Figure below.

The system of master-slave flip-flops is not restricted to J-K master-slave only. There may be an S-R master-slave or a D master-slave, etc., in all of them the slave is an S-R flip-flop, whereas the master changes to J-K or S-R or D flip-flops.

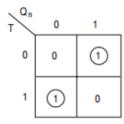

### T Flip-flop

With a slight modification of a J-K flip-flop, we can construct a new flip-flop called a T flip-flop. If the two inputs J and K of a J-K flip-flop are tied together it is referred to as a T flip-flop. Hence, a T flip-flop has only one input T and two outputs Q and Q'. The name T flip-flop actually indicates the fact that the flip-flop has the ability to toggle. It has actually only two states—*toggle state* and *memory state*. Since there are only two states, a T flip-flop is a very good option to use in counter design and in sequential circuits design where switching an operation is required. The truth table of a T flip-flop is given below:-

| T | $Q_n$ | $Q_{n+1}$ |

|---|-------|-----------|

| 0 | 0     | 0         |

| 0 | 1     | 1         |

| 1 | 0     | 1         |

| 1 | 1     | 0         |

If the T input is in 0 state (*i.e.*, J = K = 0) prior to a clock pulse, the Q output will not change with the clock pulse. On the other hand, if the T input is in 1 state (*i.e.*, J = K = 1) prior to a clock pulse, the Q output will change to Q' with the clock pulse. In other words, we may say that, if T = 1 and the device is clocked, then the output toggles its state.

The truth table shows that when T = 0, then  $Q_{n+1} = Q_n$ , *i.e.*, the next state is the same as the present state and no change occurs. When T = 1, then  $Q_{n+1} = Q'_n$ , *i.e.*, the state of the flip-flop is complemented. The circuit diagram of a T flip-flop and the block diagram of the T flip-flop is shown below:-

# **Characteristic Table of a T Flip-flop**

As we have already discussed the characteristic equation of a J-K flip-flop, we can similarly find out the characteristic equation of a T flip-flop. The characteristic table of a T flip-flop is given below. From the characteristic table we have to find out the characteristic equation of the T flip-flop.

| Flip-flop inputs | Present output | Next output |

|------------------|----------------|-------------|

| T                | $Q_n$          | $Q_{n+1}$   |

| 0                | 0              | 0           |

| 0                | 1              | 1           |

| 1                | 0              | 1           |

| 1                | 1              | 0           |

Now we will find out the characteristic equation of the T flip-flop from the characteristic table with the help of the Karnaugh map below:-

From the Karnaugh map, the Boolean expression of  $Q_{n+1}$  is derived as  $Q_{n+1} = TQ'_n + T'Q_n$ . Hence, the characteristic equation of a T flip-flop is

$$Q_{n+1} = TQ'_n + T'Q_n$$

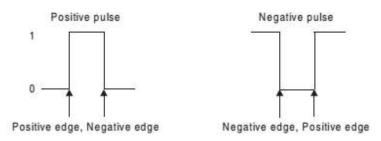

### TRIGGERING OF FLIP-FLOPS

Flip-fl ops are synchronous sequential circuits. This type of circuit works with the application of a synchronization mechanism, which is termed as a *clock*. Based on the specific interval or point in the clock during or at which triggering of the flip-flop takes place, it can be classified into two different types—*level triggering* and *edge triggering*. A clock pulse starts from an initial value of 0, goes momentarily to 1, and after a short interval, returns to the initial value.

### **Level Triggering of Flip-flops**

If a flip-flop gets enabled when a clock pulse goes HIGH and remains enabled throughout the duration of the clock pulse remaining HIGH, the flip-flop is said to be a *level triggered flip-flop*. If the flip-flop changes its state when the clock pulse is positive, it is termed as a *positive level triggered flip-flop*. On the other hand, if a NOT gate is introduced in the clock input terminal of the flip-flop, then the flip-flop changes its state when the clock pulse is negative, it is termed as a *negative level triggered flip-flop*. The main drawback of level triggering is that, as long as the clock pulse is active, the flip-flop changes its state more than once or many times for the change in inputs. If the inputs do not change during one clock pulse, then the output remains stable. On the other hand, if the frequency of the input change is higher than the input clock frequency, the output of the flip-flop undergoes multiple changes as long as the clock remains active. This can be overcome by using either master-slave flip-flops or the edge-triggered flip-flop.

# **Edge-triggering of Flip-flops**

A clock pulse goes from 0 to 1 and then returns from 1 to 0. The Figure below shows the two transitions and they are defined as the *positive edge* (0 to 1 transition) and the *negative edge* (1 to 0 transition). The term *edge-triggered* means that the flip-flop changes its state only at either the positive or negative edge of the clock pulse.

### **EXCITATION TABLE OF A FLIP-FLOP**

The truth table of a flip-flop is also referred to as the characteristic table of a flip-flop, since this table refers to the operational characteristics of the flip-flop. But in designing sequential circuits, we often face situations where the present state(PS) & the next state(NS) of the flip-flop is specified, and we have to find out the input conditions that must prevail for the desired output condition. By present and next states we mean to say the conditions before and after the clock pulse respectively. For example, the output of an S-R flip-flop before the clock pulse is Qn = 1 and it is desired that the output does not change when the clock pulse is applied.

Now from the characteristic table of an S-R flip-flop, we obtain the following conditions:

- 1. S = R = 0 (second row)

- 2. S = 1, R = 0 (sixth row).

We come to the conclusion from the above conditions that the R input must be 0, whereas the S input may be 0 or 1 (*i.e.*, don't-care). Similarly, for all possible situations, the input conditions can be found out. A tabulation of these conditions is known as an *excitation table*. The table below gives the excitation table for S-R, D, J-K, & T flip-flops. These conditions are derived from the corresponding characteristic tables of the flip-flops.

| Present       | Next              | S-R   | FF         | D- $FF$      | J-I                           | K FF    | T-FF                          |

|---------------|-------------------|-------|------------|--------------|-------------------------------|---------|-------------------------------|

| State $(Q_n)$ | State $(Q_{n+1})$ | $S_n$ | $R_{_{n}}$ | $D_{\kappa}$ | $J_{_{\scriptscriptstyle R}}$ | $K_{n}$ | $T_{_{\scriptscriptstyle H}}$ |

| 0             | 0                 | 0     | X          | 0            | 0                             | X       | 0                             |

| 0             | 1                 | 1     | 0          | 1            | 1                             | X       | 1                             |

| 1             | 0                 | 0     | 1          | 0            | X                             | 1       | 1                             |

| 1             | 1                 | X     | 0          | 1            | X                             | 0       | 0                             |

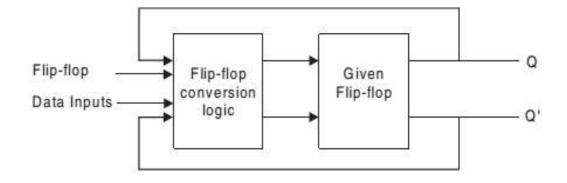

### INTERCONVERSION OF FLIP-FLOPS

In many applications, we are being given a type of flip-flop, whereas we may require some other type. In such cases we may have to convert the given flip-flop to our required flip-flop. Now we may follow a general model for such conversions of flip-flops. The model is shown in below From the model we see that it is required to design the conversion logic for converting new input definitions into input codes that will cause the given flip-flop to work like the desired flip-flop. To design the conversion logic we need to combine the excitation table for both flip-flops and make a truth table with data input(s) and Q as the inputs and the input(s) of the given flip-flop as the output(s).

# Conversion of an S-R Flip-flop to a D Flip-flop

The excitation tables of S-R and D flip-flops are given below from which we make the truth table given

| FF data inputs | Output | S-R FF inputs |   |  |

|----------------|--------|---------------|---|--|

| D              | Q      | S             | R |  |

| 0              | 0      | 0             | X |  |

| 1              | 0      | 1             | 0 |  |

| 0              | 1      | 0             | 1 |  |

| 1              | 1      | X             | 0 |  |

From the above table, we make the Karnaugh maps for inputs S and R as shown in Figure below:-

Simplifying with the help of the Karnaugh maps, we obtain S = D and R = D'. Hence the circuit may be designed as in Figure below:-

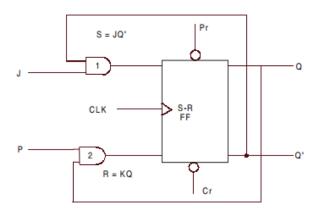

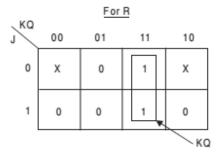

# Conversion of an S-R Flip-fl op to a J-K Flip-flop

The excitation tables of S-R and J-K flip-flops, as we studied before, from which we make the truth table given in below.

| FF dat | a inputs | Output | S-R FI | 7 inputs |

|--------|----------|--------|--------|----------|

| J      | K        | Q      | s      | R        |

| 0      | 0        | 0      | 0      | X        |

| 0      | 1        | 0      | 0      | X        |

| 1      | 0        | 0      | 1      | 0        |

| 1      | 1        | 0      | 1      | 0        |

| 0      | 1        | 1      | 0      | 1        |

| 1      | 1        | 1      | 0      | 1        |

| 0      | 0        | 1      | X      | 0        |

| 1      | 0        | 1      | X      | 0        |

From the above truth table, the Karnaugh map is prepared as shown in Figure below:-

Hence we get the Boolean expression for S and R as

$$S = JQ'$$

& R = KQ.

Hence the circuit may be realized as in below:-

# Conversion of an S-R Flip-flop to a T Flip-flop

The excitation tables of S-R and T flip-flops, as we studied before, from which we make the truth table given in below:-

| FF data inputs | Output | S-R FF inputs |   |  |

|----------------|--------|---------------|---|--|

| T              | Q      | S             | R |  |

| 0              | 0      | 0             | X |  |

| 1              | 0      | 1             | 0 |  |

| 1              | 1      | 0             | 1 |  |

| 0              | 1      | X             | 0 |  |

From the above truth table, the Karnaugh map is prepared as shown in Figure below:-

Hence we get the Boolean expression for S and R as:-

$$S = TQ'$$

and  $R = TQ$

Hence the circuit may be realized as in below:-

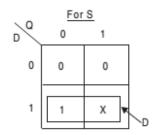

# Conversion of a D Flip-flop to an S-R Flip-flop

The excitation tables of S-R and D flip-flops, as we studied before, from which we make the truth table given in below:-

| FF date | a inputs | Output | D FF inputs |

|---------|----------|--------|-------------|

| S       | R        | Q      | D           |

| 0       | 0        | 0      | 0           |

| 0       | 1        | 0      | 0           |

| 1       | 0        | 0      | 1           |

| 0       | 1        | 1      | 0           |

| 0       | 0        | 1      | 1           |

| 1       | 0        | 1      | 1           |

From the above truth table, the Karnaugh map is prepared as shown in Figure below:-

Hence we get the Boolean expression for S and R as:-  $\mathbf{D} = \mathbf{S} + \mathbf{R'Q}$

Hence the circuit may be realized as in below:-

Similar procedure is applied for all type of Flip-Flop conversion and is left as an assignment for the student.

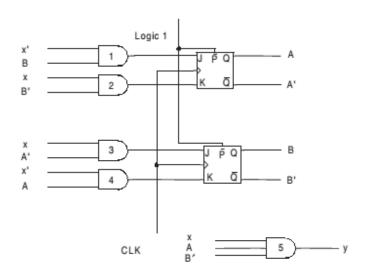

### **ANALYSIS OF SEQUENTIAL CIRCUITS**

The behavior of a sequential circuit is determined from the inputs, the outputs, and the states of the flip-flops. Both the outputs and the next state are a function of the inputs and the present state. The analysis of sequential circuits consists of obtaining a table or a diagram for the time sequence of inputs, outputs, and internal states. Boolean expressions can be written that describe the behavior of the sequential circuits. We first introduce a specific example of a clocked sequential circuit given below to understand its behavior.

### **State Table**

The time sequence of inputs, outputs and flip-flop states may be enumerated in a state table. The state table for the circuit in Figure above is shown in the table in below. Here in the table there are three sections designated as present state, next state and output. The present state designates the states of the flip-flops before the occurrence of the clock pulse. The next state designates the states of the flip-flops after the application of the clock pulse. The output section shows the values of the output variables during the present state. Again, both the output and the next state sections have two columns, one for x = 0 and the other for x = 1.

The analysis of the circuit can start from any arbitrary state. In our example, we start the analysis from initial state 00. When the present state is 00, A = 0 and B = 0. From the logic diagram, with x = 0, we find both AND gates 1 and 2 produce logic 0 signal and hence the next state remains unchanged. Also, B flip-flop for both AND gates 3 and 4 produce logic 0 signal and hence the next state of B also remains unchanged. Hence, with the clock pulse, flip-flop A and B are both in the memory state, making the next state 00. Similarly, with A = 0 and B = 0, with x = 1, we find that gate 1 produces logic 0, whereas gate 2 produces logic 1. Again, with the same condition, gate 3 produces logic 1 whereas gate 4 produces logic 0. Hence, with the clock pulse, flip-flop A is cleared and B is set, making the next state 01. This information is listed in the first row of the state table.

| Present | Next state |       | Output |       |  |

|---------|------------|-------|--------|-------|--|

| state   | x = 0      | x = 1 | x = 0  | x = 1 |  |

| AB      | AB         | AB    | у      | у     |  |

| 00      | 00         | 01    | 0      | 0     |  |

| 01      | 11         | 01    | 0      | 0     |  |

| 10      | 10         | 00    | 0      | 1     |  |

| 11      | 10         | 11    | 0      | 0     |  |

In a similar manner, we can derive the other conditions of the state table also. When the present state is 01, i.e., A = 0 & B = 1. From the logic diagram, with x = 0, we find gate 1 produces logic 1 signal and gate 2 produces logic 0. For B flip-flop both gates 3 & 4 produce logic 0 signal & hence the next state of B remains unchanged. Hence, with the clock pulse, flip-flop A is set and B remains in the memory state, making the next state 11. Similarly, with A = 0 and B = 1, with a = 1, we find that both gates 1 and 2 produce logic 0. Again, with the same condition, both gates 3 and 4 produce logic 0. Hence, with the clock pulse, both flip-flops A and B remain in the memory state, making the next state 01. This information is listed in the second row of the state table.

When the present state is 10, A = 1 and B = 0. From the logic diagram, with x = 0, we find both gates 1 and 2 produce logic 0. For B flip-flop gate 3 produces logic 0 signal but gate 4 produces logic 1. Hence, with the clock pulse, flip-flop A remains in the memory state and B is reset, making the next state 10. Similarly, with A = 1 and B = 0, with A = 1, we find that gate 1 produces logic 0, whereas gate 2 produces logic 1. Again, with the same condition, both gates 3 and 4 produce logic 0. Hence, with the clock pulse, A is reset and B remains in the memory state, making the next state 00. This information is listed in the third row of the state table.

Finally when the present state is 11, A = 1 and B = 1. From the logic diagram, with x = 0, we find gate 1 produces logic 1 and gate 2 produces logic 0. For B flip-flop gate 3 produces logic 0 signal but gate 4 produces logic 1. Hence, with the clock pulse, flip-flop A remains in the memory state and B is reset, making the next state 10. Similarly, with A = 1 and B = 1, with A = 1, we find that both gates 1 and 2 produce logic 0. Again, with the same condition, both gates 3 and 4 produce logic 0. Hence, with the clock pulse, both A and B remain in the memory state, making the next state 11. This information is listed in the last row of the state table.

The entries in the output section are easier to derive. In this example, output y = 1 only when x = 1, A = 1, and B = 0. Hence the output columns are marked with 0s except when the present state is 10 and input x = 1, for which y is marked as 1.

The state table of any sequential circuit is obtained by the same procedure used in the example. In general, a sequential circuit with m flip-flops and n input variables will have 2m rows, one for each state. The next state and output sections will have 2n columns, one for each input combination.

The external output of a sequential circuit may come from memory elements or logic gates. The output section is only included in the state table if there are outputs from logic gates. Any external output taken directly from a flip-flop is already listed in the present state of the state table.

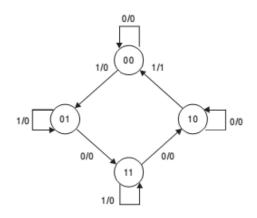

# **State Diagram**

All the information available in the state table may be represented graphically in the state diagram.

In the diagram, a state is represented by a circle and the transitions between states are indicated by direct arrows connecting the circles. The binary number inside each circle identifies the state the circle represents. The direct arrows are labeled with two binary numbers separated by a /. The number before the / represents the value of the external input, which causes the state transition, and the number after the / represents the value of the output during the present state. For example, the directed arrow from the state 11 to 10 while x = 0 and y = 0, and that on the termination of the next clock pulse, the circuit goes to the next state 10. A directed arrow connecting a circle with itself indicates that no change of the state occurs.

There is no difference between a state table and a state diagram except in the manner of representation. The state table is easier to derive from a given logic diagram and the state diagram directly follows the state table. The state diagram gives a pictorial form of the state transitions and hence is easier to interpret.

### **State Equation**

A state equation is an algebraic expression that specifies the conditions for a flip-flop state transition. The left side of the equation denotes the next state of the flip-flop and the right side a Boolean function that specifies the present state conditions that make the next state equal to 1. The state equation is derived directly from a state table. For example, the state equation for flip-flop A can be derived from the table in Figure 7.89. From the next state columns we find that flip-flop A goes to the 1 state four times: when x = 0 and AB = 01 or 10 or 11, or when x = 1 and AB = 11. This can be expressed algebraically in a state equation as follows:

$$A(t+1) = (A'B + AB' + AB)x' + ABx$$

Similarly, from the next state columns we find that flip-flop B goes to the 1 state four times: when x = 0 and AB = 01 or when x = 1 & AB = 00 or 01 or 11. This can be expressed algebraically in a state equation as follows:

$$B(t+1) = A'Bx' + (A'B' + A'B + AB)x$$

The right-hand side of the state equation is a Boolean function for the present state. When this function is equal to 1, the occurrence of a clock pulse causes flip-flop A or flip-flop B to have a next state of 1. When this function is equal to 0, the occurrence of a clock pulse causes flip-flop A or flip-flop B to have a next state of 0. The LHS of the equation identifies the flip-flop by its letter symbol, followed by the time function designation (t+1), to emphasize that this value is to be reached by the flip-flop one pulse sequence later The state equation for flip-flop A and B are simplified algebraically below. Hence, we get

$$A (t + 1) = (A'B + AB' + AB)x' + ABx$$

$$= (Bx')A' + AB'x' + AB$$

$$= (Bx')A' + (B + B'x')A$$

$$= (Bx')A' + (B + x')A$$

$$= (Bx')A' + (B'x)A.$$

If we let Bx' = J and B'x = K, we obtain the relationship: A(t+1) = JA' + KA. which is the characteristic equation of the J-K flip-flop. This relationship between the state equation and the

which is the characteristic equation of the J-K flip-flop. This relationship between the state equation and the characteristic equation can be justified from inspection of the logic diagram in the figure example of a clocked sequential circuit. In it we find that the J input of flip-flop A is equal to the Boolean function Bx' and the K input is equal to B'x.

Similarly, for flip-flop B we get

```

B (t + 1) = A'Bx' + (A'B' + A'B + AB)x

= (A'x)B' + A'Bx' + Bx

= (A'x)B' + (x + A'x')B

= (A'x)B' + (x + A')B

= (A'x)B' + (Ax')B.

```

If we let A'x = J and Ax' = K, we obtain the relationship: B(t + 1) = JB' + KB, which is the characteristic equation of the J-K flip-flop. In the diagram in example of a clocked sequential circuit, we find that the J input of flip-flop B is equal to the Boolean function A'x and the K input is equal to Ax'.

### **DESIGN PROCEDURE OF SEQUENTIAL CIRCUITS**

The design of a sequential circuit follows certain steps. The steps may be listed as follows:

- 1. The word description of a circuit may be given accompanied with a state diagram, or timing diagram, or other pertinent information.

- 2. Then from the given state diagram the state table has to be prepared.

- 3. If the state reduction mechanism is possible, then the number of states may be reduced.

- 4. After state reduction, assign binary values to the states if the states contain letter symbols.

- 5. Then the number of flip-flops required is to be determined. Each flip-flop is assigned a letter symbol.

- 6. Then the choice has to be made regarding the type of flip-flop to be used.

- 7. With the help of a state table and the flip-flop excitation table the circuit excitation and the output tables have to be determined.

- 8. Then using some simplification technique *e.g.*, a Karnaugh map or some other method, the circuit output functions and the flip-flop input functions have to be determined.

- 9. Then the logic diagram has to be drawn.

Although certain steps have been specified for designing the sequential circuit, the procedure can be shortened with experience. A sequential circuit is made up of flip-flops and combinational gates. One of the most important parts is the choice of flip-flop. From the excitation table of different flip-flops we see that the J-K flip-flop excitation table contains the maximum number of don't-care conditions. Hence, for designing any sequential circuit, it will be most simplified if the circuit is designed with, J-K flip-flop.

The number of flip-flops is determined by the number of states. A circuit may have unused binary states if the total number of states is less than 2m. The unused states are taken as don't-care conditions during the design of the combinational part of the circuit.

Any design process must consider the problem of minimizing the cost of the final circuit. The most obvious cost reductions are reductions in the number of flip-flops and the number of gates. The reduction of the number of flip-flops in a sequential circuit is referred to as the state reduction. Since m flip-flops produce 2m states, a reduction in the number of states may (or may not) result in a reduction of the number of flip-flops. State

reduction algorithms are concerned with procedures for reducing the number of states in a state table while keeping the external input-output requirements unchanged. An algorithm for the state reduction is given here. If two states in a state table are equivalent, one of them can be removed without altering the input-output relationships.

#### **SEQUENTIAL LOGIC CIRCUITS**

Now two states are said to be equivalent if, for each member of the set of inputs, they give exactly the same output and send the circuit to the same state or to an equivalent state. We will discuss the state reduction problem with an example in this section later on.

In certain cases the states are specified in letter symbols. In such cases there comes another factor, called state assignment. State assignment procedures are concerned with methods for assigning binary values to states in such a way as to reduce the cost of the combinational circuit that drives the flip-flop. For any problem there may be a number of different state assignments leading to different combinational parts of the sequential circuit. The most common criterion is that the chosen assignment should result in a simple combinational circuit for the flip-flop inputs. However, to date, there are no state assignment procedures that guarantee a minimal-cost combinational circuit.

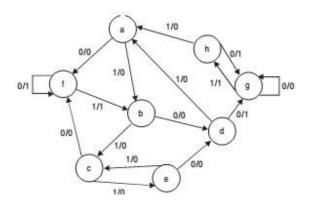

We now wish to design the clocked sequential circuit whose state diagram is given below:-

The state table for the state diagram shown above is shown in the table in Figure below.

| Present | Next s | tate  | Output |       |  |

|---------|--------|-------|--------|-------|--|

| state   | x = 0  | x = 1 | x = 0  | x = 1 |  |

| а       | f      | b     | 0      | 0     |  |

| b       | d      | c     | 0      | 0     |  |

| c       | f      | e     | 0      | 0     |  |

| d       | g      | a     | 1      | 0     |  |

| e       | d      | c     | 0      | 0     |  |

| f       | f      | b     | 1      | 1     |  |

| g       | g      | h     | 0      | 1     |  |

| h       | g      | a     | 1      | 0     |  |

We now look for two equivalent states, & find that d & h are two such states; they both go to g & a and have outputs of 1 and 0 for x = 0 & x = 1, respectively. Therefore, states d and h are equivalent; one can be removed. Similarly, we find that b and e are again two such states; they both go to d and d and have outputs of 0 and 0 for

x = 0 and x = 1, respectively. Therefore, states b and e are also equivalent; and one can be removed. The procedure of removing a state and replacing it by its equivalent is demonstrated in the table in Figure below. From the below table we find that present state c now has next states f and g and outputs 0 and 0 for g and g and g are equivalent; state g can be removed and replaced by g.

| Present | Next s | tate  | Output |       |  |

|---------|--------|-------|--------|-------|--|

| state   | x = 0  | x = 1 | x = 0  | x = 1 |  |

| a       | f      | b     | 0      | 0     |  |

| ь       | d      | e a   | 0      | 0     |  |

| g       | f      | € b   | 0      | 0     |  |

| d       | g      | a     | 1      | 0     |  |

| e       | d      | c     | 0      | 0     |  |

| f       | f      | b     | 1      | 1     |  |

| g       | g      | Кd    | 0      | 1     |  |

| K       | g      | а     | 1      | 0     |  |

The final reduced state table is shown in below:-

| Present | Next s | tate  | Output |       |  |

|---------|--------|-------|--------|-------|--|

| state   | x = 0  | x = 1 | x = 0  | x = 1 |  |

| a       | f      | b     | 0      | 0     |  |

| b       | d      | a     | 0      | 0     |  |

| d       | g      | a     | 1      | 0     |  |

| f       | f      | b     | 1      | 1     |  |

| g       | g      | d     | 0      | 1     |  |

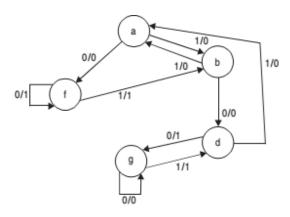

The state diagram for the reduced state table consists of only five states and is shown in Figure below:-

We now assign the different states the binary values. As we have already discussed, there may be a variety of state assignments. Some of them are shown in the below table. Among them we may choose any of them and accordingly design the circuit.

| State | Assignment 1 | Assignment 2 | Assignment 3 | Assignment 4 |

|-------|--------------|--------------|--------------|--------------|

| а     | 000          | 001          | 111          | 011          |

| ь     | 001          | 010          | 001          | 101          |

| d     | 010          | 011          | 110          | 111          |

| f     | 011          | 100          | 101          | 001          |

| g     | 100          | 101          | 010          | 000          |

In the table in Figure below, we have used binary assignment 1 to substitute the letter symbols of the five states. It is obvious that a different binary assignment will result in a state table, with completely new binary values for the states while the input-output relationships will remain the same. We will now show the procedure for obtaining the excitation table and the combinational gate structure.

| Present | Next state |       | Output |       |  |

|---------|------------|-------|--------|-------|--|

| state   | x = 0      | x = 1 | x = 0  | x = 1 |  |

| 000     | 011        | 001   | 0      | 0     |  |

| 001     | 010        | 000   | 0      | 0     |  |

| 010     | 100        | 000   | 1      | 0     |  |

| 011     | 011        | 001   | 1      | 1     |  |

| 100     | 100        | 010   | 0      | 1     |  |

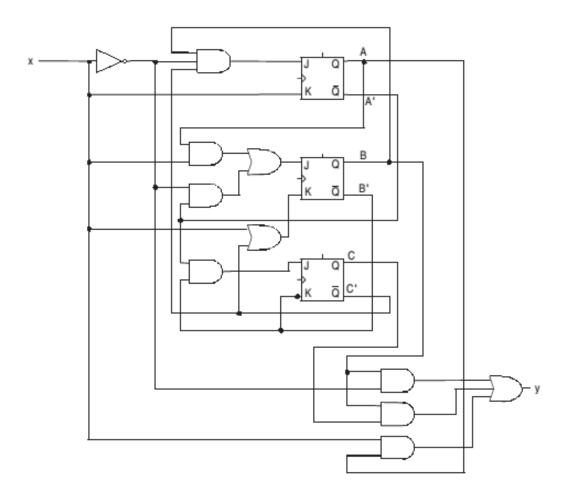

The derivation of the excitation table is facilitated if we arrange the state table in a different form. This form is shown in the below table, where the present state and the input variables are arranged in the form of a truth table. As we have previously said, we may use any flip-flop, but the simplest form of the circuit is possible with J-K flip-flops. So we now design the circuit using J-K flip-flops.

| Pre | esent st | ate | Input | $N\epsilon$ | ext stat | te |    | F  | lip-flop | input | S  |    | Output |

|-----|----------|-----|-------|-------------|----------|----|----|----|----------|-------|----|----|--------|

| A   | В        | C   | x     | A           | B        | C  | JA | KA | JB       | KB    | JC | KC | у      |

| 0   | 0        | 0   | 0     | 0           | 1        | 1  | 0  | X  | 1        | X     | 1  | X  | 0      |