# Bharath College of Science and Management, Thanjavur-5 PG Department of computer Science

Subject code : P16CSE2A

Title of the Paper : Embedded Systems

Prepared By : R. Malini,

Asst. Prof Department of Computer Science

#### UNIT-I - OVERVIEW OF EMBEDDED SYSTEMS

#### **Embedded System**

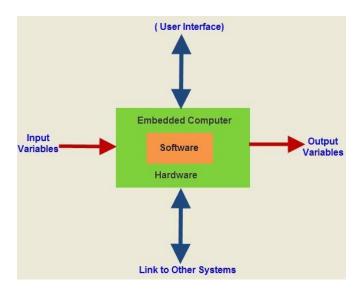

An embedded system can be thought of as a computer hardware system having software embedded in it. An embedded system can be an independent system or it can be a part of a large system. An embedded system is a microcontroller or microprocessor based system which is designed to perform a specific task. For example, a fire alarm is an embedded system; it will sense only smoke.

An embedded system has three components –

- It has hardware.

- It has application software.

- It has Real Time Operating system (RTOS) that supervises the application software and provide mechanism to let the processor run a process as per scheduling by following a plan to control the latencies. RTOS defines the way the system works. It sets the rules during the execution of application program. A small scale embedded system may not have RTOS.

So we can define an embedded system as a Microcontroller based, software driven, reliable, real-time control system.

## **Characteristics of an Embedded System**

- **Single-functioned** An embedded system usually performs a specialized operation and does the same repeatedly. For example: A pager always functions as a pager.

- **Tightly constrained** All computing systems have constraints on design metrics, but those on an embedded system can be especially tight. Design metrics is a measure of an implementation's features such as its cost, size, power, and performance. It must be of a size to fit on a single chip, must perform fast enough to process data in real time and consume minimum power to extend battery life.

- Reactive and Real time Many embedded systems must continually react to changes in the system's environment and must compute certain results in real time without any delay. Consider an example of a car cruise controller; it continually monitors and reacts to speed and brake sensors. It must compute acceleration or de-accelerations repeatedly within a limited time; a delayed computation can result in failure to control of the car.

- **Microprocessors based** It must be microprocessor or microcontroller based.

- **Memory** It must have a memory, as its software usually embeds in ROM. It does not need any secondary memories in the computer.

- Connected It must have connected peripherals to connect input and output devices.

- **HW-SW systems** Software is used for more features and flexibility. Hardware is used for performance and security.

## **Advantages**

- Easily Customizable

- Low power consumption

- Low cost

- Enhanced performance

# **Disadvantages**

- High development effort

- Larger time to market

## **Basic Structure of an Embedded System**

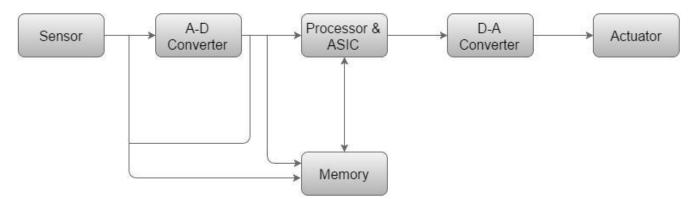

The following illustration shows the basic structure of an embedded system –

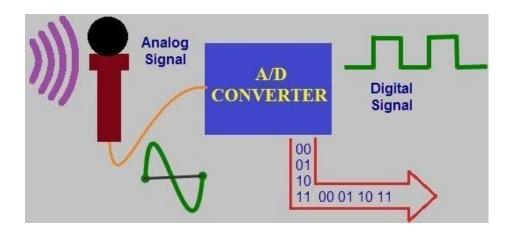

- **Sensor** It measures the physical quantity and converts it to an electrical signal which can be read by an observer or by any electronic instrument like an A2D converter. A sensor stores the measured quantity to the memory.

- **A-D Converter** An analog-to-digital converter converts the analog signal sent by the sensor into a digital signal.

- Processor & ASICs Processors process the data to measure the output and store it to the memory.

- **D-A Converter** A digital-to-analog converter converts the digital data fed by the processor to analog data

- **Actuator** An actuator compares the output given by the D-A Converter to the actual (expected) output stored in it and stores the approved output.

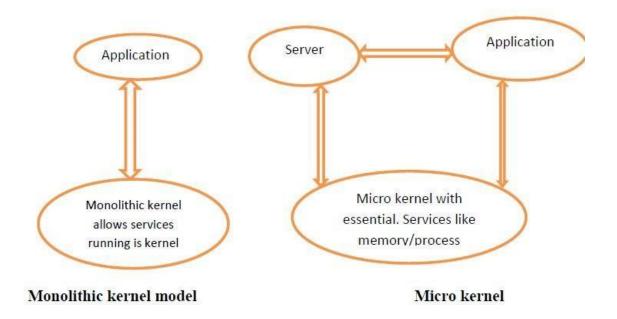

Processor is the heart of an embedded system. It is the basic unit that takes inputs and produces an output after processing the data. For an embedded system designer, it is necessary to have the knowledge of both microprocessors and microcontrollers.

## **Processors in a System**

A processor has two essential units -

- Program Flow Control Unit (CU)

- Execution Unit (EU)

The CU includes a fetch unit for fetching instructions from the memory. The EU has circuits that implement the instructions pertaining to data transfer operation and data conversion from one form to another.

The EU includes the Arithmetic and Logical Unit (ALU) and also the circuits that execute instructions for a program control task such as interrupt, or jump to another set of instructions.

A processor runs the cycles of fetch and executes the instructions in the same sequence as they are fetched from memory.

# **Types of Processors**

Processors can be of the following categories –

- General Purpose Processor (GPP)

- Microprocessor

- Microcontroller

- Embedded Processor

- Digital Signal Processor

- Media Processor

- Application Specific System Processor (ASSP)

- Application Specific Instruction Processors (ASIPs)

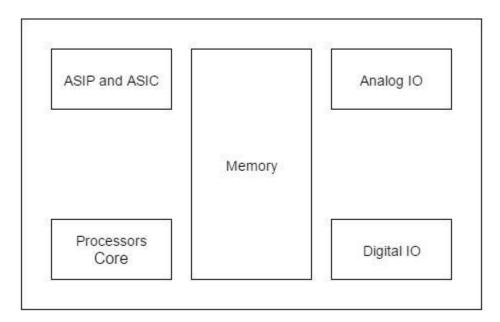

.The Embedded system hardware includes elements like user interface, Input/Output interfaces, display and memory, etc.Generally, an embedded system comprises power supply, processor, memory, timers, serial communication ports and system application specific circuits.

## **Types of Embedded Systems**

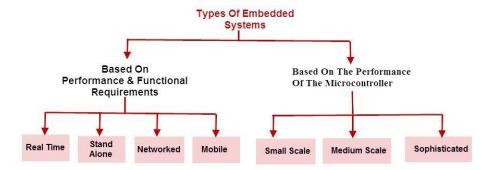

Embedded systems can be classified into different types based on performance, functional requirements and performance of the microcontroller.

# **Types of Embedded systems**

Embedded systems are classified into four categories based on their performance and functional requirements:

- Stand alone embedded systems

- Real time embedded systems

- Networked embedded systems

- Mobile embedded systems

Embedded Systems are classified into three types based on the performance of the microcontroller such as

- Small scale embedded systems

- Medium scale embedded systems

- Sophisticated embedded systems

# Stand Alone Embedded Systems

Stand alone embedded systems do not require a host system like a computer, it works by itself. It takes the input from the input ports either analog or digital and processes, calculates and converts the data and gives the resulting data through the connected device-Which either controls, drives and displays the connected devices. Examples for the stand alone embedded systems are mp3 players, digital cameras, video game consoles, microwave ovens and temperature measurement systems.

## Real Time Embedded Systems

A real time embedded system is defined as, a system which gives a required o/p in a particular time. These types of embedded systems follow the time deadlines for completion of a task. Real time embedded systems are classified into two types such as soft and hard real time systems.

#### Networked Embedded Systems

These types of embedded systems are related to a network to access the resources. The connected network can be LAN, WAN or the internet. The connection can be any wired or wireless. This type of embedded system is the fastest growing area in embedded system applications. The embedded web server is a type of system wherein all embedded devices are connected to a web server and accessed and controlled by a web browser. Example for the LAN networked embedded system is a home security system wherein all sensors are connected and run on the protocol TCP/IP

#### Mobile Embedded Systems

Mobile embedded systems are used in portable embedded devices like cell phones, mobiles, digital cameras, mp3 players and personal digital assistants, etc. The basic limitation of these devices is the other resources and limitation of memory.

#### Small Scale Embedded Systems

These types of embedded systems are designed with a single 8 or 16-bit microcontroller, that may even be activated by a battery. For developing embedded software for small scale embedded systems, the main programming tools are an editor, assembler, cross assembler and integrated development environment (IDE).

## Medium Scale Embedded Systems

These types of embedded systems design with a single or 16 or 32 bit microcontroller, RISCs or DSPs. These types of embedded systems have both hardware and software complexities. For developing embedded software for medium scale embedded systems, the main programming tools are C, C++, JAVA, Visual C++, RTOS, debugger, source code engineering tool, simulator and IDE.

#### Sophisticated Embedded Systems

These types of embedded systems have enormous hardware and software complexities, that may need ASIPs, IPs, PLAs, scalable or configurable processors. They are used for cutting-edge applications that need hardware and software Co-design and components which have to assemble in the final system.

#### **Applications of Embedded Systems:**

Embedded systems are used in different applications like automobiles, telecommunications, smart cards, missiles, satellites, computer networking and digital consumer electronics.

## **Embedded System Initialization**

It takes just minutes for a developer to compile and run a Hello World! application on a non-embedded system. On the other hand, for an embedded developer, the task is not so trivial. It might take days before seeing a successful result. This process can be a frustrating experience for a developer new to embedded system development.

Booting the target system, whether a third-party evaluation board or a custom design, can be a mystery to many newcomers. Indeed, it is daunting to pick up a programmer s reference manual for the target board and pore over tables of memory addresses and registers or to review the hardware component interconnection diagrams, wondering what it all means, what to do with the information (some of which makes little sense), and how to relate the information to running an image on the target system.

Questions to resolve at this stage are

- how to load the image onto the target system,

- where in memory to load the image,

- how to initiate program execution, and

- how the program produces recognizable output.

We answer these questions in this chapter and hopefully reduce frustration by demystifying the booting and initialization process of embedded systems.

#### **Serial Communication**

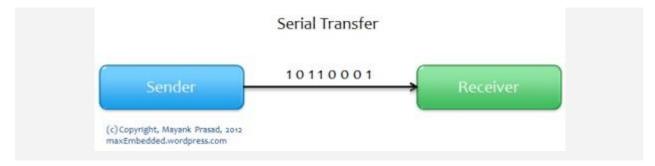

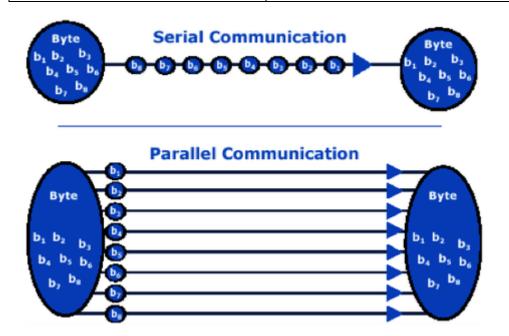

#### Serial Transfer

In Telecommunication and Computer Science, serial communication is the process of sending/receiving data in one bit at a time. It is like you are firing bullets from a *machine gun* to a target... that's one bullet at a time! ;)

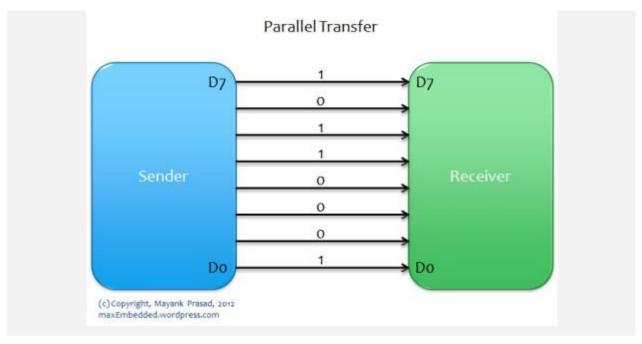

#### **Parallel Communication**

#### Parallel Transfer

Parallel communication is the process of sending/receiving multiple data bits at a time through parallel channels. It is like you are firing using a *shotgun* to a target – where multiple bullets are fired from the same gun at a time! ;)

## **Serial vs Parallel Communication**

Now lets have a quick look at the differences between the two types of communications.

| Serial Communication                               | Parallel Communication                          |

|----------------------------------------------------|-------------------------------------------------|

| 1. One data bit is transceived at a time           | 1. Multiple data bits are transceived at a time |

| 2. Slower                                          | 2. Faster                                       |

| 3. Less number of cables required to transmit data | 3. Higher number of cables required             |

# **Input/output Devices**

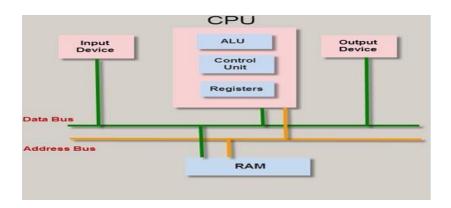

## The Address Bus

Recall from our discussion earlier about microprocessors, that every CPU has a number of pins, which work together, called an address bus. The address bus is normally used to read or write to memory, most often RAM chips. Most modern microprocessors use the address bus for more than just reading and writing to memory however.

By toggling a special pin, the CPU can switch from using the address bus for accessing RAM, to using the address bus to talk to other semi-intelligent chips that are also connected to the address bus. When used in this way, we are said to be using I/O port addressing, instead of normal memory addresses. Sometimes a port will be referred to as a register, but I find this a bit confusing, since a register normally means an internal CPU register. The semi-intelligent device chips are only activate when they detect that the special I/O pin is asserted and the address bus holds the memory value that points to that specific chip.

This is how most input and output occurs from devices like serial ports, parallel ports, floppy, hard drive and other controllers. Once the CPU has placed the proper address on the address bus and it asserts the special I/O pin, all RAM chips are temporarily disabled and the external I/O chips are read or written from instead. The bytes of data are actually transferred on a second set of pins called the data bus.

#### The Data Bus

The data bus is nothing more than a series of pins on the processor that are used to get data into, or out of, the processor chip itself. All memory and I/O devices are connected to the data bus, but depending on the current state of the address bus and other control pins on the processor, only one chip can actually be connected to the data bus at any given moment.

Depending on the exact processor used, the data bus may be 4, 8, 16, 32 or perhaps 64-bits wide. A wider data bus allows the processor to read and write more bits of data in a single operation. This technique is used with PCI-based cards on PC-compatibles to achieve faster I/O operations for certain devices. In other cases however, using more bits is a waste of time, because the device connected at the other end of the data bus only supports 4 or 8 bit transfers at a time. In this case it is very important to ignore the unused bits, generally by using a bit masking operation to force the unused bits to a zero value.

#### **Interrupt Requests**

In addition to the processor using the data bus, address bus and special I/O pin to communicate with external devices; the external devices use another pin when they need the attention of the

processor. This is referred to as an Interrupt Request Line or IRQ Line. For example, whenever you press a key on the keyboard, the keyboard controller device generally signals the main processor that a key is available by asserting the interrupt line.

The interrupt handler must be small and efficiently designed, since in some cases it could be invoked hundreds or maybe even thousands of times a second. Generally an interrupt handler performs the minimum amount of work necessary to service the device, and then exits. At that point, the processor returns to running the process that was interrupted as if nothing happened.

There are normally two different types of interrupt lines on all processors. The first is the kind we have been discussing at this point, called maskable interrupts. Maskable in this case means that interrupts can be selectively enabled or disabled by the software. The other kind of interrupt is called a non-maskable interrupt. The software can never disable this kind of interrupt. It most often used to perform the DRAM refresh on memory chips, which MUST occur at regular intervals in order to keep memory contents alive.

# Memory Mapped I/O

I/O Port addressing is not the only way the processor can communicate with external devices however. Another commonly used technique is called memory mapped I/O. In this case, instead of asserting the I/O pin and addressing a data port, the processor just accesses a memory address directly. The external device can have a small amount of RAM or ROM that the processor just reads or writes as needed.

## **Direct Memory Access**

One technique that has been used for years to speed transfer of data from main memory to an external device's memory is the direct memory access feature (DMA). The processor on the external device executes DMA transfers, without any assistance from the main processor. The processors must cooperate for this to work obviously. While the DMA transfer is in progress, the main processor is free to tend to other tasks, but should not attempt to modify the information in the buffer being transfer, until the transfer is complete.

Once the transfer is stared, the main processor is free to tend to other tasks. The external processor will take over the address and data lines periodically and execute the DMA transfer. Once the transfer is complete, the external device usually notifies the main processor of this by raising an interrupt request.

DMA's main advantage is that the main processor does not have to transfer data into one of its register, then save that to a memory address for each and every byte of data. Another advantage is the fact that whiles the DMA transfer is in progress, the CPU is free to work on other tasks. This leads to an apparently overall increase in speed.

# Synchronous, Asynchronous and Iso-Synchronous Communication

1- In **Synchronous** data transfer, each basic unit of data (such as a bit) is transferred in accordance to a clock COMMUNICATION signal or in other words the data is transferred at a pre-decided rate. So for this data transfer method a clock signal is needed. Moreover Synchronous data transfer systems usually have an error checking mechanism to guarantee data integrity over transmission.

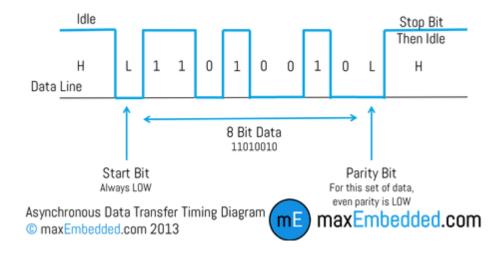

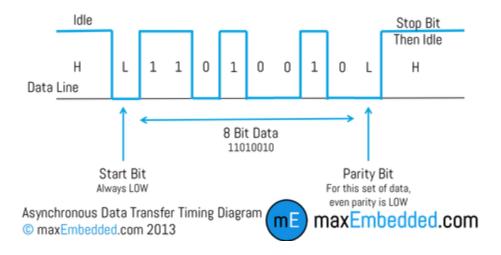

2- In **Asynchronous** data transfer systems, the data can be sent at irregular intervals and there is no pre-decided data rate of transmission. Special bits such as Start and stop bits are reserved to detect the start and end of data transmission in these systems and they are also equipped with an error checking mechanism.

3-Isochronous data transfer lies somewhat in between the two other data transmission types. It sends Asynchronous data over a Synchronous transmission system. In such systems each data source is given only a fixed time to transmit its data. In that fixed interval of time, that data source can transfer data at whatever intervals it wants. If it has data which requires less time than the time allotted then it simply wastes the extra time by staying idle. Otherwise if it has data which requires more time to transmit than given then it sends the remaining data in its next turn. These systems do not have error check mechanism because it is not possible to re-transmit the data after an error due to strict timing conditions.

Synchronous, asynchronous, and isosynchronous transmission are not three of a kind but two unrelated pairs, where the asynchronous transmission that differs from synchronous transmission may not be the same as the asynchronous transmission that differs from isosynchronous transmission. Of course, both pairs are about timing (see Chronos in Wikipedia).

# **Serial Communication Protocols**

A variety of communication protocols have been developed based on serial communication in the past few decades. Some of them are:

- SPI Serial Peripheral Interface: It is a three-wire based communication system. One wire

each for Master to slave and Vice-versa, and one for clock pulses. There is an additional SS

(Slave Select) line, which is mostly used when we want to send/receive data between multiple

ICs.

- 2 **I2C Inter-Integrated Circuit:** Pronounced eye-two-see or eye-square-see, this is an advanced form of USART. The transmission speeds can be as high as a whopping 400KHz. The I2C bus

has two wires – one for clock, and the other is the data line, which is bi-directional – this being the reason it is also sometimes (not always – there are a few conditions) called **Two Wire Interface** (**TWI**). It is a pretty new and revolutionary technology invented by Philips.

3. **FireWire** – Developed by Apple, they are high-speed buses capable of audio/video transmission. The bus contains a number of wires depending upon the port, which can be either a 4-pin one, or a 6-pin one, or an 8-pin one.

- 4. **Ethernet:** Used mostly in LAN connections, the bus consists of 8 lines, or 4 Tx/Rx pairs.

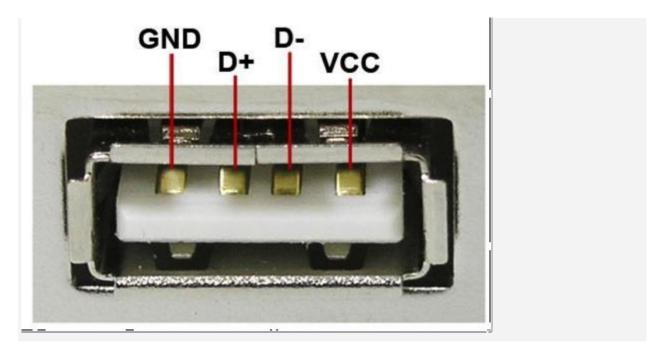

- 5. Universal serial bus (USB): This is the most popular of all. Is used for virtually all type of connections. The bus has 4 lines:  $V_{CC}$ , Ground, Data+, and Data-.

**USB** Pins

6. **RS-232** – **Recommended Standard 232:** The RS-232 is typically connected using a DB9 connector, which has 9 pins, out of which 5 are input, 3 are output, and one is Ground. You can still find this so-called "Serial" port in some old PCs. In our upcoming posts, we will discuss mainly about RS232 and USART of AVR microcontrollers.

#### Unit-II - CPU Architecture of PIC Microcontroller

**PIC Microcontroller**: PIC (Programmable Interface Controllers) microcontrollers are the world's smallest microcontrollers that can be programmed to carry out a huge range of tasks. These microcontrollers are found in many electronic devices such as phones, computer control systems, alarm systems, embedded systems, etc. Various types of microcontrollers exist, even though the best are found in the GENIE range of programmable microcontrollers. These microcontrollers are programmed and simulated by circuit-wizard software.

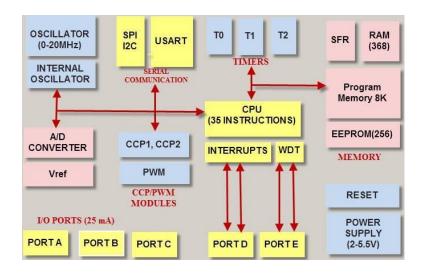

Every PIC microcontroller architecture consists of some registers and stack where registers function as Random Access Memory(RAM) and stack saves the return addresses. The main features of PIC microcontrollers are RAM, flash memory, Timers/Counters, EEPROM, I/O Ports, USART, CCP (Capture/Compare/PWM module), SSP, Comparator, ADC (analog to digital converter), PSP(parallel slave port), LCD and ICSP (in circuit serial programming) The 8-bit PIC microcontroller is classified into four types on the basis of internal architecture such as Base Line PIC, Mid Range PIC, Enhanced Mid Range PIC and PIC18

#### **Architecture of PIC Microcontroller**

The PIC microcontroller architecture comprises of CPU, I/O ports, memory organization, A/D converter, timers/counters, interrupts, serial communication, oscillator and CCP module which are discussed in detailed below.

## CPU (Central Processing Unit)

It is not different from other microcontrollers CPU and the PIC microcontroller CPU consists of the ALU, CU, MU and accumulator, etc. Arithmetic logic unit is mainly used for arithmetic operations and to take logical decisions. Memory is used for storing the instructions after processing. To control the internal and external peripherals, control unit is used which are connected to the CPU and the accumulator is used for storing the results and further process.

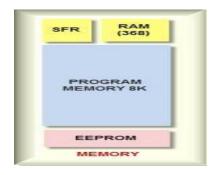

# Memory Organization

The memory module in the <u>PIC microcontroller</u> architecture consists of RAM (Random Access Memory), ROM (Read Only Memory) and STACK.

# Random Access Memory (RAM)

RAM is an unstable memory which is used to store the data temporarily in its registers. The RAM memory is classified into two banks, and each bank consists of so many registers. The RAM registers are classified into two types: Special Function Registers (SFR) and General Purpose Registers (GPR).

## **General Purpose Registers (GPR)**

These registers are used for general purpose only as the name implies. For example, if we want to multiply two numbers by using the PIC microcontroller. Generally, we use registers for multiplying and storing the numbers in other registers. So these registers don't have any special function,- CPU can easily access the data in the registers.

#### • Special Function Registers

These registers are used for special purposes only as the name SFR implies. These registers will perform according to the functions assigned to them, and they cannot be used as normal registers. For example, if you cannot use the STATUS register for storing the data, these registers are used for showing the operation or status of the program. So, user cannot change the function of the SFR; the function is given by the retailer at the time of manufacturing.

**Memory Organization**

Read Only Memory (ROM)

Read only memory is a stable memory which is used to store the data permanently. In PIC microcontrollerarchitecture, the architecture ROM stores the instructions or program, according to the program the microcontroller acts. The ROM is also called as program memory, wherein the user will write the program for microcontroller and saves it permanently, and finally the program is executed by the CPU. The microcontrollers performance depends on the instruction, which is executed by the CPU.

Electrically Erasable Programmable Read Only Memory (EEPROM)

In the normal ROM, we can write the program for only once we cannot use again the microcontroller for multiple times. But, in the EEPROM, we can program the ROM multiple times.

## **Flash Memory**

Flash memory is also programmable read only memory (PROM) in which we can read, write and erase the program thousands of times. Generally, the PIC microcontroller uses this type of ROM.

Stack

When an interrupt occurs, first the PIC microcontroller has to execute the interrupt and the existing process address. Then that is being executed is stored in the stack. After completing the

execution of the interrupt, the microcontroller calls the process with the help of address, which is stored in the stack and get executes the process.

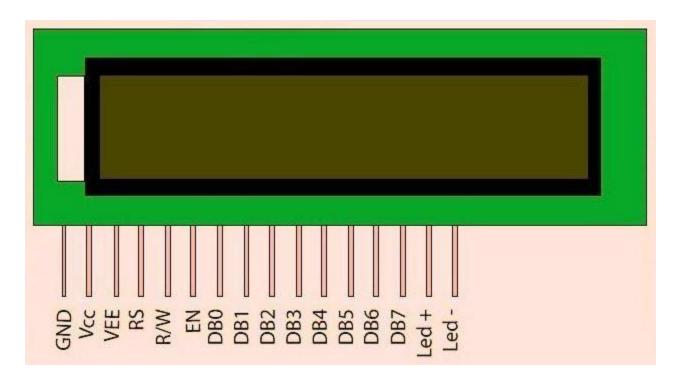

## I/O Ports

- The series of PIC16 consists of five ports such as Port A, Port B, Port C, Port D & Port E.

- Port A is an 16-bit port that can be used as input or output port based on the status of the TRISA (Tradoc Intelligence Support Activity) register.

- Port B is an 8- bit port that can be used as both input and output port.

- Port C is an 8-bit and the input of output operation is decided by the status of the TRISC register.

- Port D is an 8-bit port acts as a slave port for connection to the microprocessor BUS.

- Port E is a 3-bit port which serves the additional function of the control signals to the analog to digital converter.

#### **BUS**

BUS is used to transfer and receive the data from one peripheral to another. It is classified into two types such as data bus and address.

**Data Bus:** It is used for only transfer or receive the data.

**Address Bus:** Address bus is used to transmit the memory address from the peripherals to the CPU. I/O pins are used to interface the external peripherals; UART and USART both are serial communication protocols which are used for interfacing serial devices like GSM, GPS, Bluetooth, IR, etc.

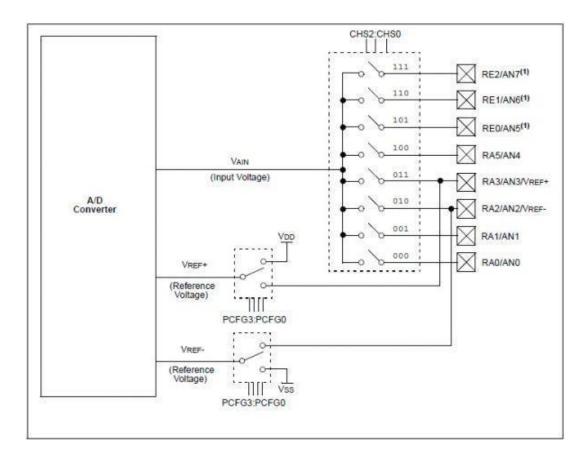

#### A/D converters

The main intention of this analog to digital converter is to convert analog voltage values to digital voltage values. A/D module of PIC microcontroller consists of 5 inputs for 28 pin devices and 8 inputs for 40 pin devices. The operation of the analog to digital converter is controlled by ADCON0 and ADCON1 special registers. The upper bits of the converter are stored in register ADRESH and lower bits of the converter are stored in register ADRESL. For this operation, it requires 5V of an analog reference voltage.

A/D CONVERTER

#### **Timers/ Counters**

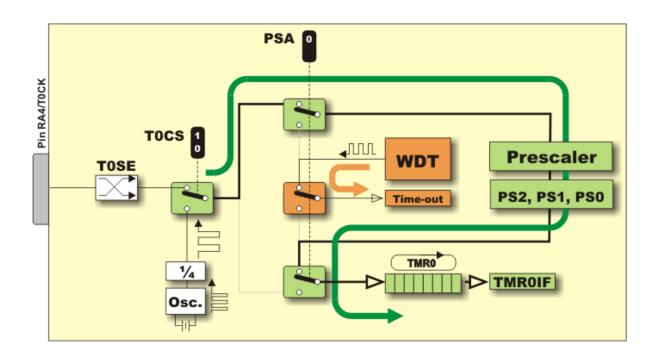

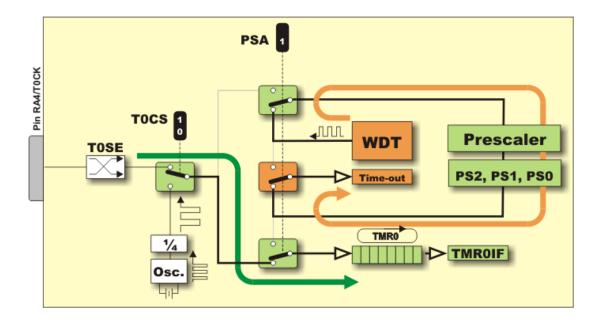

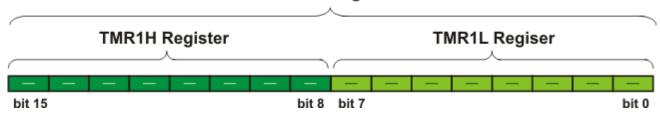

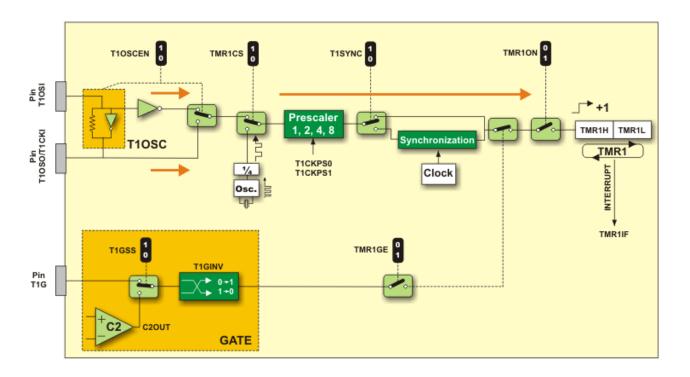

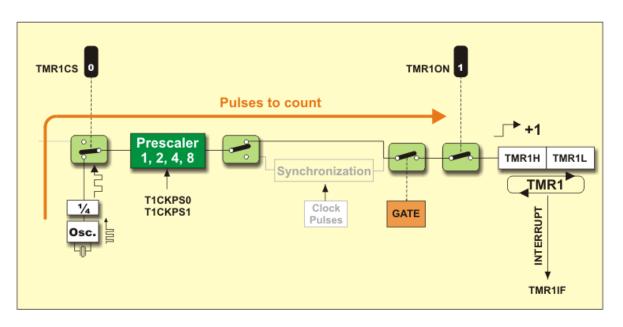

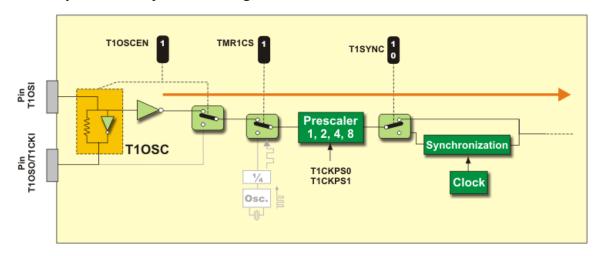

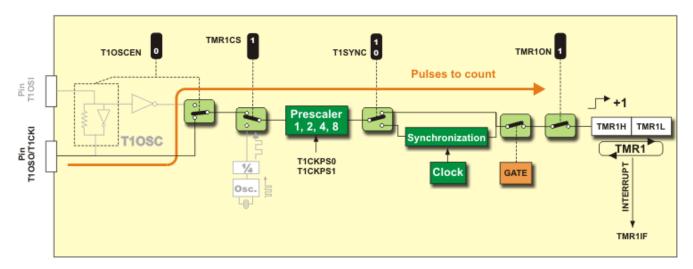

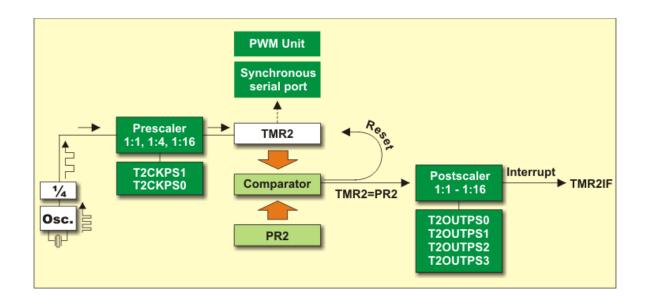

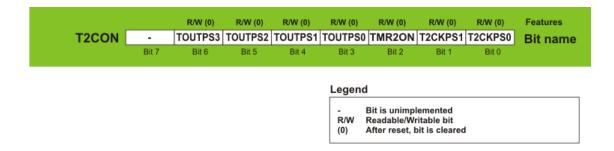

PIC microcontroller has four timer/counters wherein the one 8-bit timer and the remaining timers have the choice to select 8 or 16-bit mode. Timers are used for generating accuracy actions, for example, creating specific time delays between two operations.

## **Interrupts**

PIC microcontroller consists of 20 internal interrupts and three external interrupt sources which are associated with different peripherals like ADC, USART, Timers, and so on.

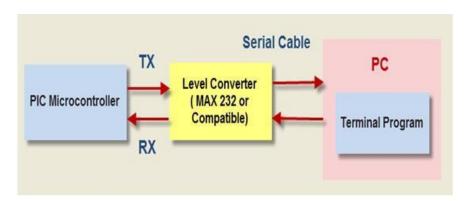

## **Serial Communication**

• **USART:** The name USART stands for Universal synchronous and Asynchronous Receiver and Transmitter which is a serial communication for two protocols. It is used

for transmitting and receiving the data bit by bit over a single wire with respect to clock pulses. The PIC microcontroller has two pins TXD and RXD. These pins are used for transmitting and receiving the data serially.

- **SPI Protocol:** The term SPI stands for Serial Peripheral Interface. This protocol is used to send data between PIC microcontroller and other peripherals such as SD cards, <u>sensors</u> and shift registers. PIC microcontroller support three wire SPI communications between two devices on a common clock source. The data rate of SPI protocol is more than that of the USART.

- I2C Protocol: The term I2C stands for Inter Integrated Circuit, and it is a serial protocol which is used to connect low speed devices such as EEPROMS, microcontrollers, A/D converters, etc. PIC microcontroller support two wire Interface or I2C communication between two devices which can work as both Master and Slave device.

**Serial Communication**

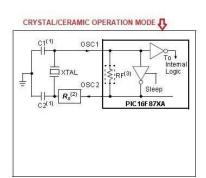

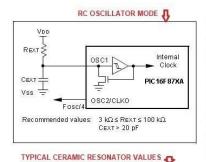

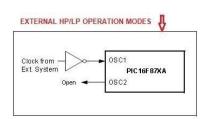

#### **Oscillators**

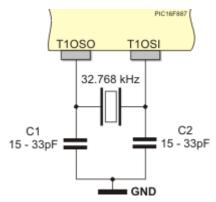

Oscillators are used for timing generation. Pic microcontroller consist of external oscillators like RC oscillators or crystal oscillators. Where the crystal oscillator is connected between the two oscillator pins. The value of the capacitor is connected to every pin that decides the mode of the operation of the oscillator. The modes are crystal mode, high-speed mode and the low-power mode. In case of RC oscillators, the value of the resistor & capacitor determine the clock frequency and the range of clock frequency is 30KHz to 4MHz.

## **CCP** module

The name CCP module stands for capture/compare/PWM where it works in three modes such as capture mode, compare mode and PWM mode.

- Capture Mode: Capture mode captures the time of arrival of a signal, or in other words, when the CCP pin goes high, it captures the value of the Timer1.

- **Compare Mode:** Compare mode acts as an analog comparator. When the timer1 value reaches a certain reference value, then it generates an output.

- **PWM Mode:** PWM mode provides pulse width modulated output with a 10-bit resolution and programmable duty cycle.

## **PIC Microcontroller Applications**

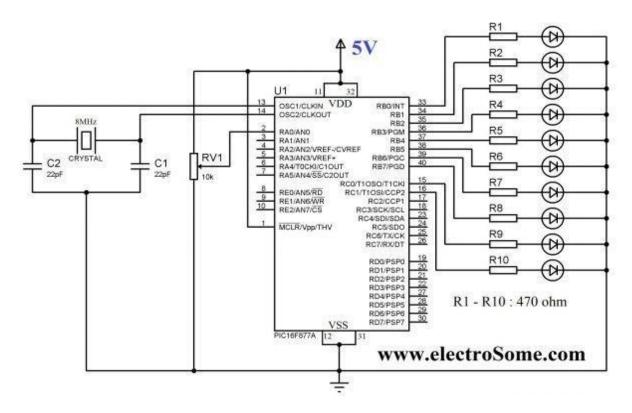

The PIC microcontroller projects can be used in different applications, such as peripherals, audio accessories, video games, etc. For better understanding of this PIC microcontroller, the following project demonstrates PIC microcontroller's operations.

#### Street Light that Glows on Detecting Vehicle Movement:

The main intention of this project is to detect the movement of vehicles on highways to switch on a block of street lights ahead of it, and also switch off the trailing lights to conserve energy. In this project, a PIC microcontroller is done by using assembly language or embedded C.

The power supply gives the power to the total circuit by stepping down, rectifying, filtering and regulating AC mains supply. When there are no vehicles on highway, then all lights will turn OFF so that the power can be conserved. The <u>IR sensors</u> are placed on the road to sense the vehicle movement. When there are vehicles on highway, then the IR sensor senses the vehicle movement immediately, it sends the commands to the PIC microcontroller to switch ON/OFF the LEDs. A bunch of LEDS will be turned on when a vehicle come near to the sensor and once the vehicle passes away from the sensor the intensity will become lower than the LEDs will turn OFF

#### **Advantages of PIC Microcontroller:**

- PIC microcontrollers are consistent a**nd** faulty of PIC percentage is very less. The performance of the PIC microcontroller is very fast because of using RISC architecture.

- When comparing to other microcontrollers, power consumption is very less and programming is also very easy.

- Interfacing of an analog device is easy without any extra circuitry

# Disadvantages of PIC Microcontroller:

- The length of the program is high due to using RISC architecture (35 instructions)

- One single accumulator is present and program memory is not accessible

#### **Reset Function**

Reset function is one of the most advanced features that is available on all modern microcontrollers. The PIC16F8xx series have various kinds of resets. The various kinds of reset options that are available on PIC 16F877 series are given below.

- Power-on Reset (POR).

- MCLR Reset during normal operation.

- MCLR Reset during Sleep.

- WDT Reset (during normal operation).

- WDT Wake-up (during Sleep).

- Brown-out Reset (BOR).

A simplified block diagram of the on-chip Reset circuit is shown in the figure below. his document contains very brief examples of assembly language programs for the x86. The topic of x86 assembly language programming is messy because:

- There are many different assemblers out there: MASM, NASM, gas, as86, TASM, a86,

Terse, etc. All use radically different assembly languages.

- There are differences in the way you have to code for Linux, OS/X, Windows, etc.

- Many different object file formats exist: ELF, COFF, Win32, OMF, a.out for Linux, a.out for FreeBSD, rdf, IEEE-695, as86, etc.

- You generally will be calling functions residing in the operating system or other libraries

so you will have to know some technical details about how libraries are linked, and not

all linkers work the same way.

- Modern x86 processors run in either 32 or 64-bit mode; there are quite a few differences between these.

We'll give examples written for NASM, MASM and gas for both Win32 and Linux. We will even include a section on DOS assembly language programs for historical interest. These notes are not intended to be a substitute for the documentation that accompanies the processor and the assemblers, nor is it intended to teach you assembly language. Its only purpose is to show how to assemble and link programs using different assemblers and linkers.

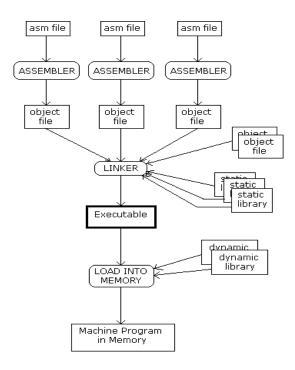

#### **Assembler linkers**

Each assembly language file is assembled into an "object file" and the object files are linked with other object files to form an executable. A "static library" is really nothing more than a collection of (probably related) object files. plication programmers generally make use of libraries for things like I/O and math.

## Assemblers you should know about include

- <u>MASM</u>, the Microsoft Assembler. It outputs OMF files (but Microsoft's linker can convert them to win32 format). It supports a massive and clunky assembly language. **Memory addressing is not intuitive.** The directives required to set up a program make programming unpleasant.

- **GAS**, the GNU assember. This uses the rather ugly AT&T-style syntax so many people do not like it; however, you can configure it to use and understand the Intel-style. It was designed to be part of the back end of the GNU compiler collection (gcc).

- NASM, the "Netwide Assembler." It is free, small, and best of all it can output zillions of different types of object files. The language is much more sensible than MASM in many respects.

There are many object file formats. Some you should know about include

- **OMF**: used in DOS but has 32-bit extensions for Windows. Old.

- **AOUT**: used in early Linux and BSD variants

- **COFF**: "Common object file format"

- Win, Win32: Microsoft's version of COFF, not exactly the same! Replaces OMF.

- Win64: Microsoft's format for Win64.

- **ELF, ELF32**: Used in modern 32-bit Linux and elsewhere

- **ELF64**: Used in 64-bit Linux and elsewhere

- macho32: NeXTstep/OpenStep/Rhapsody/Darwin/OS X 32-bit

- macho64: NeXTstep/OpenStep/Rhapsody/Darwin/OS X 64-bit

#### **Oscillator Selection Function**

The PIC16F8xx series basically supports different types of oscillators and also PIC16F87XA devices. It also has a Watchdog Timer which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability (Configurations as compared to normal microcontrollers/processors). The different oscillator modes can be easily selected by the user. The user can program two configuration bits (foscillator1 and foscillator0) to selection of the basic four modes. The basic oscillator modes and the typical values used for these oscillators are given in the picture below.

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High-Speed Crystal/Resonator

- RC resistor/capacitor oscillator

| ОѕсТуре | Crystal<br>Freq.              | Cap. Range<br>C1            | Cap. Range<br>C2 |  |

|---------|-------------------------------|-----------------------------|------------------|--|

| LP      | 32 kHz                        | 2 kHz 33 pF                 |                  |  |

|         | 200 kHz                       | 15 pF                       | 15 pF            |  |

| XT      | 200 kHz                       | 47-68 pF                    | 47-68 pF         |  |

|         | 1 MHz                         | 15 pF                       | 15 pF            |  |

|         | 4 MHz                         | 15 pF                       | 15 pF            |  |

| HS      | 4 MHz                         | 15 pF                       | 15 pF            |  |

|         | 8 MHz                         | 15-33 pF                    | 15-33 pF         |  |

|         | 20 MHz                        | 15-33 pF                    |                  |  |

|         | ues arefor o<br>following thi | design guidance<br>s table. | only.            |  |

|         | Cry                           | stals Used                  |                  |  |

| 32 kHz  | Epson C-001R32.768K-A         |                             | ± 20 PPM         |  |

| 200 kHz | STD XTL                       | ± 20 PPM                    |                  |  |

| 1 MHz   | ECS E                         | ± 50 PPM                    |                  |  |

| 4 MHz   | ECS E                         | ± 50 PPM                    |                  |  |

| 8 MHz   | EPSON CA                      | ±30 PPM                     |                  |  |

|         |                               | EPSON CA-301 20.000M-C      |                  |  |

| Mode    | Freq.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OSC1                    | OSC2             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|

| XT      | 455 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68-100 pF               | 68-100 pF        |

|         | 2.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15-68 pF                | 15-68 pF         |

|         | 4.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15-68 pF                | 15-68 pF         |

| HS      | 8.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10-68 pF                | 10-68 pF         |

|         | 16.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-22 pF                | 10-22 pF         |

| F       | FOR DESIGN U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VANEDOOT AREAS          |                  |

| F       | Control of the Contro | ISE ONLY<br>itors Used: |                  |

| 2.0 MHz | Resona                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VANEDOOT AREAS          | ± 0.5%           |

|         | <b>Resona</b><br>Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tors Used:              | ± 0.5%<br>± 0.5% |

| 2.0 MHz | Resona<br>Murata Erie<br>Murata Erie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tors Used:<br>CSA2.00MG |                  |

Ranges Tested

circuitstoday.com

#### **UNIT-III-PIC PROGRAMMNG**

#### **INTERRUPTS**

Interrupt is the signal which is sent to the microcontroller to mark the event that requires immediate attention. This signal **requests** the microcontroller to stop to perform the current program temporarily **time** to execute a special code. It means when external device finishes the task imposed on it, the microcontroller will be notified that it can access and receive the information and use it. Interrupts are just like waiting for the phone to ring.

#### **INTERRUPT SOURCES in microcontrollers**

The request to the microcontroller to stop to perform the current program temporarily can come from various sources:

- Through external hardware devices like pressing specific key on the keyboard, which sends

Interrupt to the microcontroller to read the information of the pressed key.

- During execution of the program, the microcontroller can also send interrupts to itself to report an error in the code. For example, division by 0 will causes an interrupt.

- In the multi-processor system, the microcontrollers can send interrupts to each other to communicate. For example, to divide the work between them they will send signals between them.

#### **INTERRUPT TYPES in PIC microcontrollers**

There are 2 types of interrupts for PIC microcontroller that can cause break.

**Software Interrupt:** It comes from a program that is executed by microcontroller or we can say that it is generated by internal peripherals of the microcontroller and requests the processor to hold the running of program and go to make an interrupt.

**Hardware Interrupt:** These interrupts are sent by external hardware devices at certain pins of microcontroller.

# **External interrupt of PIC18F452 microcontroller**

**External INTERRUPT IN PIC18F452:** Sometimes External devices are connected with **microcontroller**. If that external device has to send some information to microcontroller, then microcontroller needs to know about this situation to get that information. An example of such external device is the **digital thermometer**. It measures the **temperature** and at the end of measurements transmits results to the microcontroller. Now the purpose of this article to explain the fact that how does the microcontroller knows to get the required information from external device.

## **Types of interrupts**

There are two methods of communication between the microcontroller and the external device:

- By using Polling

- By using Interrupts

#### **POLLING**

In this method, the external devices are not independent. We fix the time interval in which microcontroller has to contact the external device. The microcontroller accesses that device at the exact time interval and gets the required information. Polling method is just like picking up our phone after every few seconds to see if we have a call. The main drawback of this method is the waste of time of microcontroller. It needs to wait and check whether the new information has arrived not.

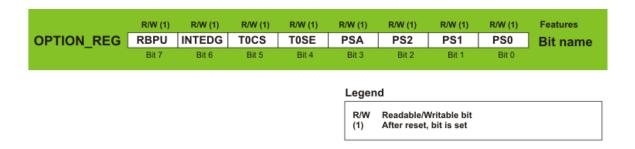

# **REGISTER CONFIGURATION for external interrupt**

These are the registers for interrupt operation and minimum 1 register can be used to control the interrupt operation in PIC18F452 which are:

- RCON (Reset Control Register)

- INTCON, INTCON2, INTCON3 (Interrupt Control Registers)

- PIR1, PIR2 (Peripheral Interrupt Request Registers)

- PIE1, PIE2 (Peripheral Interrupt Enable Registers)

## **RCON Register:**

- Reset control register

- IPEN bit to enable interrupt priority scheme, 1= enable priority level on interrupts

- Other bits used to indicate the cause of reset

RI (Reset Instruction flag), TO (Watchdog Time Out flag), PD (Power on Detection flag),

POR (Power on Reset status) and BOR (Brown Out Reset status bit)

## **INTCON Register:**

- 3 Interrupt control registers INTCON1, INTCON2, INTCON3

- Readable and writable register which contains various enable and flag bits

- Interrupt flag bits get set when an interrupt condition occurs

- Contain enable, priority and flag bits for external interrupt, port B pin change and TMR0 overflow interrupt

## **PIE Register:**

- Peripheral Interrupt Enable register

- May be multiple register (PIE1, PIE2), depending on the number of peripheral interrupt sources

- Contain the individual bits to enable/disable Peripheral interrupts for use

#### **PIR Register:**

- Peripheral Interrupt Flag register

- May be multiple register (PIR1, PIR2), depending on the number of peripheral interrupt sources

- Contain bits to identify which interrupt occurs (flags)

- Corresponding bits are set when the interrupt occurred

# **EXTERNAL INTERRUPT registers setting**

INTCON registers are just used to configure the external PIC interrupts. This article also deals with external interrupts of PIC18F452 so we will discuss it in detail here..

#### FOR PERIPHERAL INTERRUPT:

The PIE (Peripheral Interrupt Enable) and PIR (Peripheral Interrupt Request) registers are used to configure the Peripheral (Internal) Interrupts.

INTCON REGISTER:

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RAIE  | TOIF  | INTF  | RAIF  |

## **GIE: Global Interrupt Enable**

This bit is set high to enable all interrupts of PIC18F452.

- 1 = Enable all interrupts

- 0 =Disable all interrupts

# **PEIE: Peripheral Interrupt Enable**

This bit is set high to enable all the peripheral interrupts (Internal interrupts) of the microcontroller.

- 1 = Enable all peripheral interrupts

- 0 = Disable all peripheral interrupts

## **T0IE: TMR0 Overflow Interrupt Enable**

This bit is set high to enable the External Interrupt 0.

- 1 = Enable TMR0 overflow interrupt

- 0 = Disable TMR0 overflow interrupt

## **INTE: INT External Interrupt Enable**

This bit is set high to enable the external interrupts.

- 1 = Enables the INT external interrupt

- 0 = Disables the INT external interrupt

## **RBIE: RB Interrupt Enable**

This bit is set high to enable the RB Port Change interrupt pin.

- 1 = Enables the RB port change interrupt

- 0 = Disables the RB port change interrupt

## **T0IF: TMR0 Overflow Interrupt Flag**

- 1 = TMR0 register has overflowed (it must be cleared in software)

- 0 = TMR0 register has not overflowed

## **INTF: INT External Interrupt Flag**

- 1 = The INT external interrupt occurred (it must be cleared in software)

- 0 =The INT external interrupt did not occur

# **RBIF: RB Port Change Interrupt Flag**

- 1 = At least one of the RB7:RB4 pins changed the state (must be cleared in software)

- 0 = None of RB7:RB4 pins have changed the state

## **INTCON2 REGISTER:**

| R/W-1 | R/W-1   | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-1   | 0-0 | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0 | R/W-1 |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|