### Embadded System

origanizing are during one are may cost according to a fixed plan, program or set of rules

which all its unit assumbles and work together according to the plan are program

ore wasting Machine, Digital Comora,

It is a time display system. It's par are its hardware, needles and buttery with the beautiful dial, chassis and with the beautiful dial, chassis and strap. This parts organize to show strap. This parts organize to show seed time overy second and continously real time overy second.

### Embadded System:

An embadded system is a system that has embadded software and computer handware which makes its a system dedicated for an application or or specific part of a application or product or a part of a larger system

DODD D. MORTEN Author of embadded micro controller:

Embodded systems are electronic System that contain a microprocesso? or micro contraller. But be do not thing of them as computer. The computer is hidden or embadded sixte

David E. Simon

people use the term embaddes system to mean any computer system hidden in any of this products.

Embadded

the standard the standard

1 1 4

An ambadded Sesstem is a Sesster that has three main components ambadded into it.

It embadder hardware Semilar to

As its Software usually embaddes in the ROH or flash memory its regulally do not need a secondary hard digk CD, Memory as un a Competer. T. L. ... L. mit

It ambadder main application Softmore . The application softmore may concountly portor a series of tasts or processor or thoroads. It ambadded a real time operating System the supericisor the application software running as hardware and organizas acides to a regounce according to the propriorit at tasks in the segstern or processor embadded into a system, Embadded processor in a System GU LA DEXEC [control unit] [Execution unit] processor is a chip CIC) model Processor core form: ASI -> Application specific Integration SOC -> System On a chip VLSI -> Vary Large Scale Integration 2020/05/16 15:52

General purpose processor CGPP):

Micro processor

Embaddal processor

Application Specific instraction Set production (ASIP):

Micro controller

Embadded micro controller

Digital Signal processor (GSP)

and Media processor

Network processor and I/o process

Single purpose processor (SPP) as addition Processors:

Co processor: digital number

Accelerator: eg: Java Code

controller: eg: peripharal device

GPP (or) ASIP Cosses Integrated

into either an ASIP a VLSI circuit

Application specific system

processor

Multicone processor

Microprocesor:

One and only CPV NOT used in RAM & ROM

~4 MHZ it is yearly

Advanced in 4 GHZ Intel 80 × 86. use of ambadded system ARM, 68 HCXXX, 80X86, SPARC many coul from Microcontroller: 8085, ARH, Intal, philips, samsung Single purpose processor. 1. co processor og floating paint 2. Graphics processor processor image: 144 × 176 pixal -> CIF smage video graphic: 640 x 480 pixel vide o frame 525 x 625 pixal 3 ipjed coprocessor: Display high resolution picture formats -> 2592 × 1944 4. Encryption engine 5. Decryption engine 6. A discreate consire transfor COCT) speech and video processing 7. protocol Stack processor

8. Natuosk processor Connection establish Data sort and receive process q. Accelerator Real time process 10. CODEC Cocaden and Docaden) 11. JPEGI CODEC; Joint photographic Export Group 12. MPEG: (Motion pictures exports (nor oup) 13. Controllers eg: (peripharal deciles

ASIC: Application Specific Integration circuit:

An application specific internated

The components that can soc generally loops to incorporate with in ilself include a control processing unit input and output ports interval mornory. I'm it had have

VLSI: Very Large Scale Integration:

VLST is the process of creating an integrated circuit by combining thousan of transisters into Single chip The micro processor is a ULSI doese

embadded hardware units and desice in a system: J. C. L. 11 10 1

i) pourer source:

Some Systems are directly connect not direct connect custo pourer source NIC -> Naturosk Interface card

1.5. OUT 0.25U 33 UT 0.3V 2.0VI. 0.2V 1.4. 1.50± 0.20

we can also use charge pemp ii) clock oscillator and clocking curits:

clock in objected signals controls time to executing an

instruction

iii) System timen:

configured for system clock system superinter denction in the

### 4. Road time clock:

incuit for the counting and timing down

5. Reset circuit, power -up Reget and watching - Timer Reget:

From the beginning using a switch

beginning whenever power is Suitched as in the System.

Restart at System when it is Stuck up in certain Set of instructions for a period more than a proset time internal.

Embadded software in a System:

Final trachine implement software for a system.

crecities softmane Had in specific to a

in the final splace or place in ROM

on that momory - the software

alto called FOH image.

each coole are datum in available only in the bits and byte dormat. The segetom requires byte at each ROM address according to the task being executed.

a moline in along to ble on Otion

software in a processor specific assembly larguages: -A program are a small specific part an be coded in assembly language cesting a assembler after condenstanding the processor and its instruction set assembler the software aged for developing code in assembly. Assembly language coding is extraamly aseful for configuring physical douice like codes à like display ADC and DAC and reading into or transmitting from a buffer Machine Machine codes Assembles the program at various Machine random speadic for loading Asjembly at variou anguage -Address program prom library ju Bytes for heeded marchie thinked Davie (ROH) Data Byles

Data Byles

Program

Rom monony

On on marambles I wantete the resembly we otherwise into the trench cooler curing a teter rallal assouth 6 In the word stop lufting cadlod a linton links the cooler with the other cortes nequinal unting is no cossess be come at the number of codes to be link for the final binning file + The linted like in binary for noun. a computer of commonly knowsh executed file or sinply an @ In the next stop

| e 13 | Dructwal               | with in a                                | oreo@88धाः :                      |

|------|------------------------|------------------------------------------|-----------------------------------|

| 9    | In dural               | wite                                     | functions                         |

|      | MOR                    | Manoney                                  | I thould the bytes                |

|      |                        | P.ogiston                                | or word to be                     |

|      | 1 1 1                  | h la | It halds begte or                 |

|      | 14%-R                  | Data<br>poguster                         | I soman external                  |

|      | 4. 觀(古)<br>日 [1] 中 (1) |                                          | Address.                          |

|      | System                 | Internal Bus                             | It oretenrolly                    |

|      | Luzoz                  | 1 mm X2                                  | connects all the structural write |

|      | 1. 1.1/                | and the second                           | inside the processor              |

|      | 2 4                    | 7                                        | 3, 18, 32, 48 (or)                |

|      | 1.1                    | Address Bu                               |                                   |

|      | 7 7018 10              | 4                                        | address from Ath                  |

|      |                        |                                          | and other units                   |

| 14   |                        | ## ## f <sup>37</sup>                    | 1 CHENOM                          |

|      | 5 (A 16)               | Data Bus                                 | An external during                |

|      | 17.1                   |                                          | a good or with                    |

| -1,  | 1 . J. J.              | An all the                               | operation or to                   |

|      |                        |                                          | an acc                            |

|      |                        |                                          | 2020/05/16 16:00                  |

2020/05/16 16:00

the address in determined by HER on viteral set of signal to consider cont control bus signal to precedent ex namos of deside BIU - Bus Interface vist: an intenface with between processon internal unite and victorial buses IR - Instruction Register: I + Sequentially takes instruction codes (OP code) to procution wit of P.co 1058 0x ID - Instruction Dedector:-It decodes the instruction receive at He IR and pupper it to processor CPU die- entros cu - contral unit :-It contrals all the bus admitted and unit functions needed for procking ARS- Application Register set: (0) A set of on chip register reced during processing of instruction of an application program (or) b) A regular windows (c) a serbret as registe with soch subject satisfy variably afa software routing d) A societer file associ

2020/05/16 16:00

to a cuit seich as Plu or FLPU.

ALU - Assistantic Logical unit:

A unit to execute arithmetic or

logical instructions according to

the current instructions present

at IR.

### PC - Program counter:

It generates an instruction cycle by Sending the address defined by it to memory through MAR-It autoincrements as the instruction autoincrements as the instruction are fetched regularly and Sequentially it is called instruction pointer in 80×86 processors.

### SP - Stack pointer: -

A pointer for an address which corresponts to a stack-top in memory.

### IR - Instruction Queue:-

He IR does not have to wait for the rest instruction after one has been processed: It sequentially stores, like an instruction queue, the instructions in

MMU- Memory Maragement unit: \_ It marages the marnories such that the instruction and data randi available processing.

SRS-System Register Set:

It is a set at registers cused while processing the instructions of the Supereisery System program.

FLPU-Floating point processing unit:

A curit separate from ALV for Floating point processing which is essential in processing functions fast in a micro processor.

FRS-Floating Point Register Get:A projector set dedicated for Storing floating point numbers in a standard format and used by FLPU for its data and stack.

Allocation of mamory to program segement and blocks and memory map of a system.

17 @ Functions. Processor data and stacks at the various segment

=> Program soutines and process and have different Segements

For example.

and each segement stored at a different beforementy block

A pointer address points to the start of the memory block storing a segement and an off set value a segement and an off set value it used to retrines for a memory address with in that segement

the data have also the sagement at different blocks an

A segement, have portions at fixed sixed screek called pages.

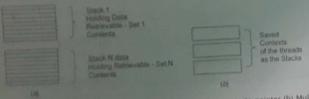

Segement types 19 code Stock Extra Date. 200 monte of gorgt. y or e Cover 1 offing aronge page Inames cogenest permitted Mamory blocks for elements at the different data structure and data set. the software design approach isto use data sote and data christine in a program Their can be different sets and different structures of data Following of the data structur at the memory. and data sale that are commonly used during processing in a system. A) A spata structure called stack in a special program alamant: i) A stact means on alloted themory block from autich al date . + in allows we in a LIFO

| weary by the processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| stack holding 2 byto noddress that po sapring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| date sotionable blocks  an LIFO Mode start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Stock bolding date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Retrievable Set Content  Stact - N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Petrievable Set - 11 Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Samed<br>Contexto<br>of the<br>Task of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| The state of the s |

of each processor has alleged one short pointer so that the withintion slow con be prenter on calling of the rountines can be fachiliated

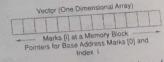

B) The date structure array is an important programing alament MCOJ, HCIJ ... MCNJ one diencersiand array is a special date structure at the mornory. It has a position address that always points to the first element of the assing

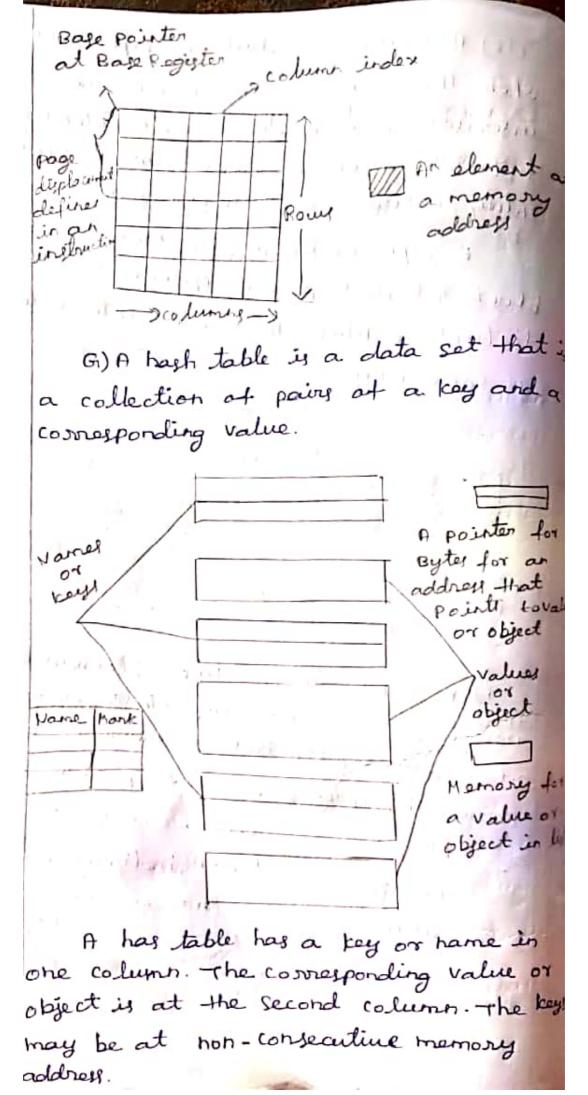

C- Marks Cizos a memory Block Base Address Hort Coj 6

ii) A data structure called a queue in another impostant programming alement iv) circular queue.

v) queue pipe

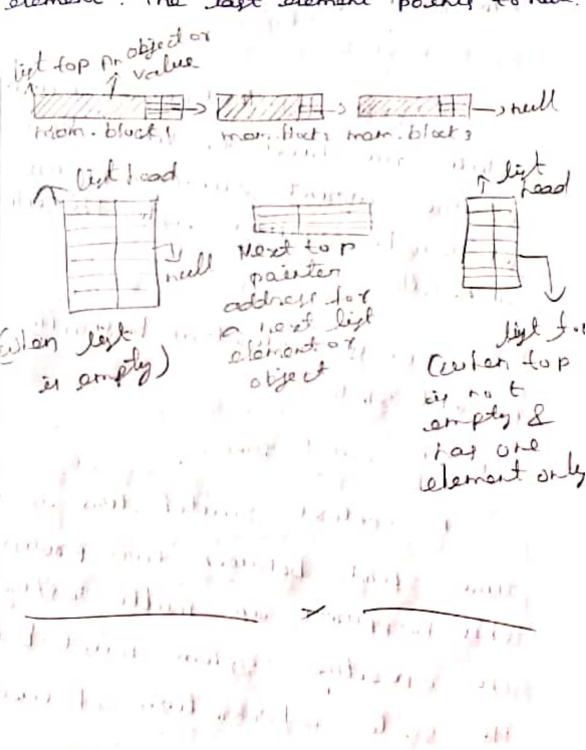

Vii) hash table (pair of key 26000003vi) table - poreling values)

viii) list

It means an allotted memory block from which a date element is always ratriaced in FIFO.

Hoad and the other for its tail.

ouch addition. It is called quare back or tail pointer.

The other pointer is for painting to an address in a memory block from where an element can be deleted to it called queue front or head pointer. I just position

Stack Delated to act Black Pointer pointer quone for adding addresses into quent

DA circular queue is a queue in which both pointers cannot increment beyond the memory block and reset to starting value on insertion beyond the boundary

Start

() I queue is called a pipe, generally when the source from where the inscritions are made has an identity distinct from a distination ( sint) entity where delation are made. A pipe means a common memory block allotted for a queue to two distinct antities that are interconnected in some way. d. prodat tack & Defeting from pipe Tout! End Back Start Debted pointer Pointer from adding into pipe pipe F) A table is a two-dimensional array and is an important data er Set that is allocated a marrowy block. - phone is always a bone pointer for - phere are two indicines are for a table. a column & other for a you. 2020/05/16 16:06

H) A list in a data structure with number at memory blocks, one for each element.

A list has a top painter for the memory address from where it starts tack list element at the memory also stores the pointer to the next element. The last element points to rull.

### **INTERRUPT-SERVICING MECHANISM**

A service routine executes on interrupt.

### 6.7.1 Preventing Interrupts Overrun

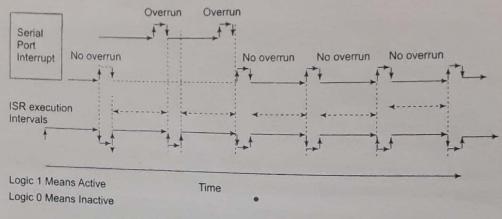

When a source causes an interrupt then execution of corresponding ISR services the request made through the interrupt. When interrupt from the same source reoccurs then that also needs to be serviced. Overrun means that the processor has not completed execution of an ISR for the earlier interrupt before a new one from that source reoccurred.

### Example 6.11

- 1. Assume that the port is receiving bits every 1 µs, 1 byte in 8 µs and the next byte starts after 8 µs. When a new interrupt occurs before the previous byte saves then serial interrupt overrun occurs.

- 2. Assume that a synchronous serial port interrupt occurs. If another source interrupted before the service of serial interrupt starts, and ISR for other source could not complete and before second serial interrupt occurs then interrupt overrun occurs.

- 3. A user inserts the coin in an automatic chocolate-vending machine, and the user inserts another coin before the ISR corresponding to earlier inserted coin finishes then interrupt overrun occurs.

Figure 6.15 shows the interrupt overrun situation for serial port interrupts.

Interrupt overrun can be prevented by several methods. One method is when an ISR is servicing, disable other interrupts.

Fig. 6.15 Interrupt overrun of serial port interrupts

### Disabling Interrupts 6.7.2

When a routine or ISR is executing in the codes, which must be completed because interrupt from same source is expected soon after, and the situation of interrupt overrun is likely to occur then an instruction DI (Disable Interrupts) is executed at the beginning of the ISR and EI (Enable Interrupts) is executed

When a routine or ISR is executing codes in a critical section of codes, which must completed because if another routine starts then situation of interrupt overrun is likely to occur then an instruction DI is executed at the beginning of the critical section of codes and EI at the exit from the section is executed.

### Example 6.12

- 1. A microcontroller, device or system can have interrupt-control bit, one-bit EA (Enable All). EA is called primary level disabling or enabling bit. Resetting the EA bit disables complete interrupt

- 2. A microcontroller, device or system has individual interrupt-control bits for different interrupt sources or different groups with similar sources in one group. The bits are called secondary level disabling or enabling bit. Resetting one of the bits disables corresponding source or group of similar sources. Setting one of the bits enables corresponding source or group of similar sources.

### Nonmaskable Interrupts and Maskable Interrupts Concept & 6.7.3

Masking an interrupt means when interrupt takes place, the service to that interrupt-request does not occur. Maskable sources of interrupt provides for masking and unmasking the interrupt service

### Example 6.13

Nonmaskable: Examples are RAM parity error in a PC and error interrupts like division by zero. These

Maskable: Execution of a device interrupt source or source group can be masked by the corresponding interrupt-control bit. An interrupt request at external signal (at pin) can be masked. An interrupt request execution of a trap can be masked. An interrupt request execution of a software interrupt (exception function or signal function) can be masked. Most interrupt sources are maskable,

A few specific interrupts cannot be masked and they are called nonmaskable interrupts. Nonmaskable interrupts are those for which the service is uninterrupted. Maskable interrupts are those for which the service may be temporarily interrupted to let other ISRs execute till it is masked.

### Interrupt Status Register or Interrupt Pending Register

An identification of source of an interrupt is required, for the processor to interrupt and to initiate steps for servicing of the interrupt. A processing system can identify interrupt by status flag corresponding to an interrupt source in a processor status register. A flag (bit) in status register can identify the interrupt

A bit in interrupt-pending register that corresponds to an interrupt source enables a processor to when that is set. interrupt when the processor is not executing any other interrupt whose priority is higher than that.

### Example 6.14

- 1 The 8051 SCON register status bits are RI and TI to identify the status of serial receive and serial transmit register. A common ISR executes when either TI or RI sets in. An ISR Instruction is used 后,明色代明中国。2015年,1915年,1915年中国的第一年,1915年中国的第一年,1915年中国的第一年,1915年,1915年中国的1915年,1915年中国1915年,1915年中国1915年,1915年中国1915年,1915年中国1915年,1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年中国1915年 to reset the flag.

- 2. The 8051 TCON register has TFO and TF1 flag bits for timer 0 overflow and timer 1 overflow interrupt. TFO auto-resets when ISR corresponding to TO overflow start execution. TF1 auto-resets when ISR corresponding to T) overflow start execution,

### 6.7.5 Interrupt Vector

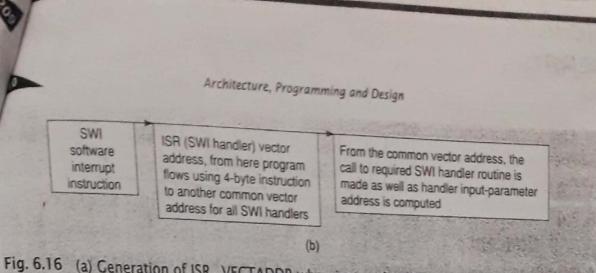

An interrupt vector is a memory address to which processor vectors [transfers to instruction pointer (program counter) new address] on an interrupt. It then services the interrupt by executing ISR either (i) starting at that address, (ii) at address pointed and generated by bytes at that address, or (iii) starting at that address and then the ISR instruction points to the new ISR address corresponding to the source of interrupt or bits specified in the SWI instruction.

### Example 6.15

1. The 8051 services the hardware interrupts by executing ISR starting at ISR\_VECTADDR address. The 8051 processor generates distinct ISR VECTADDR addresses for INTO, TO, INTL. TI, Serial and T2. 2. The 8086 services the interrupt by executing ISP, at address pointed and generated by bytes address generated from n in INT n instruction or hardware interrupt corresponding to a specified n. Figure 6-16(a) shows generation of ISR VECTADDR when instruction INT n'executes for interrupting the processor. 3 Figure 6.16(b) shows the use of ISR. VECTADDR in APM for the jump to the routine for the interrupt servicing when SWI kinstruction executes, where his a set of bits. The bits are used in instructions which calculate new starting address of ISR for SWI and calculate pointer to the ISR Input parameters. ISR VECTADDR is common to all values of A ISR\_VECTADDRn Processor finds the ISR vector address INTn from the four bytes at ISR\_VECTADDRn address which computes from n Each hardware or software interrupt source has a type n (a)

Fig. 6.16 (a) Generation of ISR\_ VECTADDR when instruction INT *n* executes for interrupting the processor (b) Use of ISR\_ VECTADDR in ARM for the jump to the routine for the interrupt servicing when SWI I instruction executes

### Interrupt Vector Table

An Interrupt vector table is a concept used for programming for the service routines of each interrupt source. Interrupt vector table means a table of ISR\_VECTADDR addresses for each interrupt source. The processor interrupts and execute ISR correspond to that address. A table facilitates locating the codes of the ISRs at ISR\_VECTADDRs. Figure 6.17 shows concept of a vector table in memory in case of multiple interrupt-sources or source groups.

ISR VECTADDR 1 From a vector address either the 4-ISR VECTADDR 2 or 8-byte short ISR Devices vector addresses of interrupts ISR VECTADDR 3 executes or a Jump from the hardware interrupt sources ISR\_VECTADDR 4 instruction executes ISR\_VECTADDR 5 for the long ISR codes at a new ISR\_VECTADDR 6 starting address

Fig. 6.17 Concept of vector table in memory in case of multiple interrupt-sources or source groups

An interrupt vector is an important part of interrupts-service mechanism, which associates a processing system. The processor first saves instruction pointer (program counter) and/or other registers of CPU on interrupt and then loads a vector address into the program counter. Vector address has (i) ISR, (ii) ISR address for the processor for interrupt source or interrupt type, or a group of sources. Interrupt vector table is an important part of interrupts service mechanism, which provisions for multiple interrupt sources and source groups.

### Example 6.16

Consider a touch screen. It generates an interrupt when a screen position is touched. Interrupt activates a request IRQ to the touch-screen controller. A status bit  $b_t$  also sets. The  $b_t$  resets on start of ISR<sub>IRQ</sub>. It is a service function (get\_touch\_position). It reads ADC input. The input gives the touched screen position using a look-up table. The look-up table consists of touched screen positions for each ADC input value.

Controller sends the touched position to the system. System has a table consisting of the previous command(s) and next command for each touched positions. Actions are taken as per the command.

### 6.8 MULTIPLE INTERRUPTS

### 6.8.1 Multiple Interrupt Calls

When there are the multiple interrupt sources, an occurrence of each interrupt source (or source group) is identifiable from a bit or bits in the status register and/or in the IPR.

There can be interrupt-service calls in case the higher priority interrupt source activates in succession.

A return from any of the ISR is to the lower priority pending ISR.

Let us understand the processor interrupt-service mechanism for the case of multiple interrupts. There can be two types of processor actions to handle multiple interrupts.

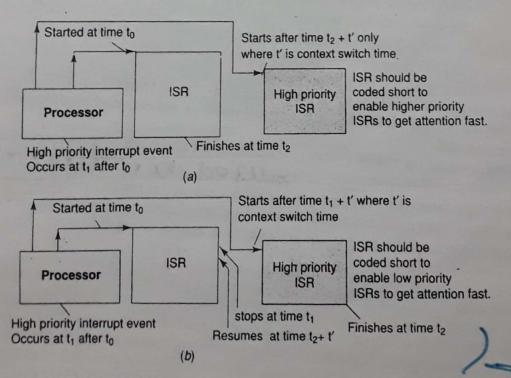

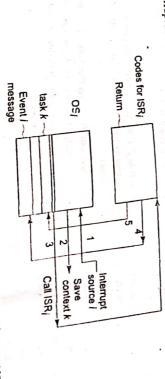

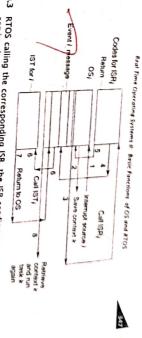

1. Certain processors do not provide for in-between routine diversion to higher priority interrupts unless all interrupts or interrupts of priority greater than the presently running routine are masked. Diversion is called *context switching* of processor. Figure 6.18(a) shows diversion to higher priority interrupts only at the end of present interrupt-service routine.

2. Certain processors permit in-between routine diversion to higher priority interrupts. Figure 6.18(b) shows the actions in case the processor provides in diversion in-between the running ISR. There is provision for disabling or masking all interrupts by primary level bit when prevention is needed for in-between diversion. These processors also provide ways to prevent diversion in between the running ISR selectively by provisioning for masking selectively the interrupt service by secondary level bits for the ISR interrupt source groups.

Fig. 6.18 (a) Diversion to higher priority interrupts, only at the end of the present interrupt service routine (b) In-between routine diversion to higher priority interrupts unless all interrupts or interrupts of priority greater than the presently running routine are masked

6.10 Find the address (instruction pointer) from where a new program begins Currence out processor status word,

Process of change of running program at the CPU to a new program is as follows: A. Save the address (instruction pointer) from where the program will begin on return and save

2. Save current program's registers, and other program parameters

A Load the program's address into instruction pointer (program counter),

Load the new program's status word, registers, and other program parameters, and

6. Execute instructions of the new program. [Program means foreground program, process, thread, task, routine, ISR, signal handler or exception handler.]

6.20(a) shows current program context. on return, processor-status word, current program's registers, and other program parameters, Figure 6.20(a) shows current program content Context of a program means, the address (instruction pointer) from where the program will begin

new program context. Figure 6.20(b) shows steps on context switching when new program executes Steps 1 and 2 mean, saving the currently running program context. Steps 4 and 5 mean loading the

from same state as at the instance of earlier change from the program. same state as at the instance of change to new program, (ii) when new program starts then it also starts Context saving is essential. The process ensures that (i) on return the saved program starts from

Context switching is performed in the system when

K foreground program interrupts and ISR starts execution

When an ISR interrupts by higher priority ISR and new ISR starts

When returning to previously running program,

lon

When a signal is issued and signal handler executes When an exception is thrown on exceptional condition and exception handler (catch function) executes, and

Figure 6.20(c) shows context switching to new routine and another switch on return to current routine. When a thread (or task or process) starts waiting for a message or parameter and blocks, and system software starts new thread. - well ed to mullet tal Jell

Figure 6.20(d) shows context switching for a new routine and another switch on higher priority routine. loading the new context. Context switching period equals the processor time spent in saving the context plus time taken in

routine)]. Context saving on the call of another program is essential before switching to another context. Context loading is essential so that a new one starts from the previously left context. Program Each running program has a context at an instant. Context reflects a CPU state [instruction pointer, means foreground program, process, thread, task, routine, ISR, signal handler or exception handler. stack pointer(s), registers and program state (variables that should not be modified by another

### INTERRUPT LATENCY

is called interrupt latency. after context switching. The interval between occurrence of interrupt and start of execution of the ISR When a processor interrupts the service of the interrupt by execution, the ISR may not start immediately

CONTEXT AND THE PERIODS FOR CONTEXT SWITCHING and Subustine the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the address financing program at the CPU to a new the cPU to a new the address financing program at the CPU to a new the Current Program context PC (Program counter) Processor status register CPU registers SP (stack pointer) 1 Save current routine context on stack and load new routine context Context Switching at I, Execute new routine codes On return save new routine context and switch for the previous routine by retrieving the saved context program ISR or Context Switching Starts after time to + I' where I' is context switch time Steps on switching for new routine priority ISP. Higher Current routine Context Switching at 12 Save current function or ISR con and load sext function or ISR con priority ISR Starts after time le + f where t is context switch time

Fig. 6.20 (a) Current program context (b) Steps on context switching when new program switch on higher priority routine on return to current routine (d) Context switching for new routine and another executes with new context (c) Context switching to new routine and another switch

1. When the interrupt service starts immediately on context switching, the interrupt latency =  $T_{\text{gwitch}}$  = context switching period. When instructions in a processor takes variable clock cycles, maximum clock cycles for an instructions are taken into account for calculating latency. Figure 6.21(a) shows latency in case of interrupt service starts immediately.

When the interrupt service does not start immediately by context switching, but context switching starts after all the ISRs corresponding to the higher priority then the interrupts complete the execution and processes. If sum of the time intervals for completing the higher priority routines =  $ST_{exec}$  then interrupt latency =  $T_{switch}$  +  $ST_{exec}$ . Figure 6.21(b) shows latency in case of interrupt service starts after ISRs of higher priority, before the present interrupt baishes the execution.

3. Interrupt system disabling instruction disables any other process of ISR from running when a routine enters a critical section and disabling instruction enables the processes or interrupts when the routine exits the critical section codes. The  $T_{disable}$  is the period for which a routine is disabled in its critical section and may or may not be included depending upon the programmer's approach The interrupt service latency from the routine with interrupt-disabling instruction (due to presence

Scanned with CamScanner

Architecture, Programming and Design

### PROGRAMMING IN ASSEMBLY LANGUAGE (ALP) AND IN HIGH-LEVEL LANGUAGE 'C'

### 7.1.1 Assembly Language Programming

Assembly-language coding of an application has the following advantages:

- 1 Assembly codes are rensitive to the processor, memory, ports and devices. Assembly software gives a precise control of the processor internal devices, and makes full use of processor-specific

- gatures of processor instruction set and addressing modes. 2 Machine codes are compact, and are processor and memory sensitive. The system thus needs a smaller memory. No additional memory need due to data type's selection, conditions, and declarations of rules. A program is also not compiler specific and library-function specific.

- 3. Certain codes such as device-driver codes may need only a few assembly instructions. Assembly codes for these can be compact and precise, and are conveniently written.

- A. Bottom-up-design approach is easily usable. Approach to this way of designing a program is as follows. First code the basic functional modules (submodules) and then use these to build a bigger module. Submodules of the specific and distinct sets of actions are first coded. Programs for delay, counting, finding time intervals and many applications can be written. Then the final program is designed by integrating the modules.

High-level lampance coding of source files in C, C++, C#, Visual C++, or Java provides great programming case, and has many advantages. Therefore, most embedded programming is in the high-lavel language. Basic advantages are as follows:

Program-development cycle is much shorter in high-level language even for complex systems due to the following: use of (i) routines (procedures) [called functions in C/C++ and methods in Javaj. (ii) standard library functions, and (iii) modular programming, top-down design and object oriented design approaches. Application programs in high-level language are structured. This ensures that the software is based on sound software engineering principles. Application programs in high-level language are structured. This ensures that the software is based on sound software engineering principles. Application programs are application programs. are programmed using given operating system, file systems, device drivers and network drivers, and have access to devices by generic functions. Application program uses Application Program Interfaces (APIs), which makes task of development of an application simple.

This days always programming approach, used in high-level language is as follows: Main program.

Interfaces (APIs), which makes task of development of an application simple.

2. Top-down-design programming approach, used in high-level language is as follows: Main program is designed first, then its modules, submodules, and finally, the functions.

3. A high-level language program facilitates declaration of data types. Type declarations simplify the programming. Each data type is an abstraction for the methods, which are permitted for using. The program facilitates declaration as a let of permissible operations on that data.

4. The program facilitates 'type checking'. This makes a program less prone to error. For example, type checking does not permit subtraction, multiplication and division on the char data types.

- type checking does not permit subtraction, multiplication and division on the char data types

- 5. The program facilitates use of program-flow-control structures, such as loops and conditional

- 6. The program has portability, and is not processor specific. Therefore, when hardware changes, only the modules for the device drivers and device management, initialisation and program-locator modules, and initial boot-up record data need modifications. OS takes care of these functions. Additional advantages of C as a high-level languages are as follows:

Programming Concepts and Embedded Programming in C, C++ and Java

It is a language between low (assembly) and high-level language, Inserting the assembly language codes in between is called *in-line assembly*. A direct hardware control is thus also feasible by in-line assembly, and the complex part of the program can be in high-level language.

### Example 7.1

- Square root is a library function. Use of standard square root () function saves the programmer

- Square root is a library function. Use of standard square root () function saves the programmer time for coding.

Four types of integers are int, unsigned int, short and long. When dealing with positive only values at type variable is declared as unsigned int. Number officks to a clock, numTicks is an unsigned data type variable is declared as unsigned integer. Arithmetical calculations use signed integer, int (32-bit). An integer can also be declared as following data types, short (46-bit) of long (64-bit).

A data type is char for manipulating text of a string of characters.

A data type is char for manipulating text of a string of characters.

Control structures widely used are while, do-while, break and for and conditional statements widely used are [if-fiese, else-if and switch-case.

Type checking permits operator to be used for concatenation when using int, unsigned int. shorf and long type of the concatenation operation. Can be understood as follows: The micro + controller concatenation operation. Can be understood as follows: The micro + controller concatenation operation. Can be understood as follows: The micro + controller concatenation operation. Can be understood as follows: The micro + controller concatenation operation. Can be understood as follows: The micro + controller where will be understood as follows: The micro + controller where will be understood as follows: The micro + controller concatenation operation, can be understood as follows: The micro + controller where will be understood as follows: The micro + controller concatenation operation, can be understood as follows: The micro + controller concatenation operation.

High-level language programming makes the program-development cycle short, enables use of the modular-programming approach, and lets us follow sound software-engineering principles. It facilitates the program development with tors down design approach. Embedded evident program development with tors down design approach. facilitates the program development with top-down-design approach. Embedded system programmers have sized long preferred C for the following reasons: (i) Feature of embedding assembly cardasses in have since long preferred C for the following reasons: (i) Feature of embedding assembly codes using incline assembly and (ii) Readily available modules in C compilers for the embedded system and in-line assembly, and (ii) Readily available modules in C compilers for the embedded system and library codes that can directly port into the custom-programmer codes. library codes that can directly port into the system-programmer codes.

### 'C' PROGRAM ELEMENTS: HEADER AND SOURCE FILES AND PREPROCESSOR DIRECTIVES

- $A \cdot C$  program has the following structural elements:

- 1. Preprocessor declarations, definitions and statements,

- Include directives for the file inclusion

The finitions for preprocessor global variables (global means all throughout the program module)

Definitions of constants

Association for proper described the first property of the program module)

Association for property described the first property of the first property of the program module)

- Definitions of constants

Peclarations for global data types, type declaration and data structures, macros and functions of program elements, header and source files and preprocessor directives are as follows:

Include Directive for the Inclusion of Files

Include is a preprocessor-directive to include the contents (codes or data) of a file. The files that can be included as given below. Inclusion of all files and specific header files has to be as per requirements.

A 'C' program first includes the header and source files. The garm small the qualitable files. The purpose

A 'C' program first includes the header and source files. These are readily available files. The purpose of each included file is mentioned in the comments within the /\* and \*/ symbols as per practice in C

Scanned with CamScanner

230

Architecture, Programming and Design

### Example 7.2

- include "vxWorks h"/\* Include VxWorks functions "/

Include "semLib.h"/\* Include Semaphore functions Library "/

Include "semLib.h"/\* Include Semaphore functions Library "/

Include "magQLib.h"/\* Include Message Queue functions Library "/

Include "magQLib.h"/\* Include Message Queue functions Library "/

Include "follb.h"/\* Include system library for system functions "/

Include "systib.c"/\* Include system library for system functions "/

Include "netDrvConfig.txt"/\* Include a text file that provides the "Network Driver Configuration". It

Include "netDrvConfig.txt"/\* Include a text file that provides the "Network Driver Configuration" and the state frame format protocol (SLIP or PPP or Ethernet) description, card description/make, address at the system, IP address (s) of the node (s) that drive the card for transmitting or receiving from the network."/

Include "pretiltandlers.c"/\* Include file for the codes for handling and actions as per the protocols

- # include "prctlHandlers.c"/\* Include file for the codes for handling and actions as per the protocols used for driving streams to the network, \*/

- Including Codes Files These are the files for the codes already available. For example,  $\emptyset$  include "pretifiantlers.c".

- Including Constant Data Files These are the files for the codes and may have the extension

- Including Strings Data Files These are the files for the strings and may have the extension 'strings' or 'str' or '.txt. For example, # include "netDrvConfig.txt"

- Including Initial Data Files \_ Initial or default data files are for locating in ROM of embedded-system. Boot-up program is copied later into RAM and has extension, '.init'. On the other hand, RAM data files have the extension, '.data'

- Including Basic Variables Files Files for the local or global static variables are stored in RAM. Variables do not possess initial (default) values. Static means that there is a common not more than one instance of that variable at memory address and it has a static memory allocation. There is only one real-time clock in the system. Therefore, only one instance of that variable address exists.

These basic variables are stored in the files with the extension 'bss'.

- fincluding Header Files It is a preprocessor directive. It includes the contents (codes or data) of a set of source files. These are files for specific modules. A header file has the extension 'h'.

### Example 7.3

- A preprocessor directive is '\$ include <marh.h>' for including standard library functions for mathematical operations in a program. Programs using mathematical expressions need mathematical functions, square root, sin, cos, tan, atan and so on. Functions become available by including a header file, called "math.h".

A preprocessor directive is '\$ include <astring.h>' for including standard library functions for the strings in a program. Programs using strings need string manipulation functions. These become available once a header file called "string.h" is included.

A program includes header files for the codes in assembly, I/O operations (conlo.h), OS or RTOS functions. \$ioolide "www.hs.h.h" is directive to compiler, which includes VxWorks RTOS functions. [Certain compilers provide for conlo.h in place of stalo.h. This is because embedded systems usually do not need the file functions for opening, closing, read and write operations using the computer keyboard and video monitor. So including stalo.h file, makes the code too larger.]

Programming Concepts and Embedded Programming in C, C++ and Java What is the difference between inclusion of a header file, and a text file or data file or consider inclusions. What is the difference between inclusion of a header file, and a text file of usual file of considerate.

Consider inclusions of netDrvConfig.txt and math.h. (i) The header files are well tested and deby consider inclusions of netDrvConfig.txt and math.h. (ii) The header files are usual files of the consideration includes. (iii) The header files provide access to standard libraries. consider inclusions of nelDrvConfig.txt and math.h. (1) The licauer lifes are well usual and deby modules. (ii) The header files provide access to standard libraries. (iii) The header files provide access to standard libraries. (iii) The header files provide access to standard libraries. (iii) The header file specific information of text for specific information. nequies. (ii) The header files provide access to standard libraries. (iii) The header file cases several text file or C files, (iv) A text file is just a description of text for specific information.

Source files are program files for the functions of application software. The source files need to be compiled, tested and validated. A source file also necesses the preprocessor directives of applications. source rites are program files for the functions of application software. The source rites need to be compiled, tested and validated. A source file also possesses the preprocessor directives of application software. The file has the first function (main function) from where the processing will start. The endcompiled, tested and validated. A source file also possesses the preprocessor directives or application software. The file has the first function (main function) from where the processing will start. The code in C for first function is void main (). The main function calls other functions.

Configuration files are the files for the configuration of a subsystem. Device configuration codes can be put in a file of basic profession right. eoninguration these are the files for the configuration of a subsystem. Device config

### (3)

A preprocessor directive starts with a sharp (hash) sign. These commands are for the following a directive to the compiler for processing.

Preprocessor Global Variables For example, in a program "# define time"

Preprocessor Constants with a sharp (hash) sign. These commands are for the following a sharp that the fo

- Preprocessor Constants "# define false 0" is a preprocessor directive in an example. It

neans it is a directive before processing to assume 'false' as 0. "# define pt 3.147"

Strings can also be defined. Strings are the constants, for example, those used for an initial displace on the screen in a mobile system. For example, # define welcome "Welcome To ABC Telegon". on the screen in a mobile system. For example, # define welcome "Welcome To ABC Telecom Embedded C programs use preprocessor constants, variables, and inclusion of configuration files, toy files bands files configuration."

- text files, header files and library functions.

### PROGRAM ELEMENTS: MACROS AND FUNCTIONS

Table 7.1 lists the uses and other features of programming elements called macros and functions.

Table 7.1 Uses of macros and functions

| Program<br>Element | Uses                                                                                                                                                                                                                                | Saves context on the stack be-<br>fore its start and retrieves them<br>on return | Feasibility of<br>nesting one<br>within another                      |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Macro              | Executes a named small collection of codes.  Executes a named set of codes with values or references to the values passed from the calling function through its arguments. Also returns data when function is not declared as void. | Yes, Each function has the context saving and retrieving overheads.              | Yes, can call<br>another function<br>and can also be<br>interrupted. |

17.00

( page )

and typodol. Mast function exercises a

sessed set of codes, calls a set of flow

and interrupts for convenient lively

and processed organization after the belowper then it enters who seems when the contribution function is called rooms and flow than STREET IN COURT PROVIDENCE OF TAKES

Secure and place property to secretary other, Afficial the object, see that orders or our sufferent varioathast ng paint And succession is returned out of

With the Car Parket grand by a

SPECIES OF SERVICES You, has the wonders saving and

> sections function Yes to another re-

Yes, has the country away and

To ESS of higher ent danned

Topopora and Depart of

the property of the property of the party of named in case of the sale and the sale when the sale is not to be sale of the A commendation of the party of

Buckfoods Toy pass pur forming done Success worth and every care and substant toke so water and ones or state of the state

ung Concepts and Embedded Programming in C, C++ and Java

How does a macro differ from a function?

1. The codes for a function are compiled only once. Processor has to save the context on calling that calls [The brackets for the function calls are not optional.] or structure]. For example, the enable PortA Intr ( ) and disable\_PortA Intr ( ) are the function data. [Primitive means similar to an integer or character. Reference type means similar to an array (wold declaration case) or return a Boolean value, an integer, or any primitive or reference type of function, and on return, processor restores the context. Further, a function may return nothing

The codes for Macro are compiled in every function wherever that macro name is used. Compiler a function, the processor does not save the context, and thus does not have to restore the context. before compilation, puts the codes at the places wherever the macro is used. When a macro runs in

3. Macros are used for short codes only. This is because, if a function call is used for short codes of short codes within a function. We use a function for codes when the  $I_{overheads} << I_{ecos}$  and a macro for codes when  $I_{outleads} = ot > I_{con}$ additional time,  $T_{eventuals}$ . The time is the same order of magnitude as the time,  $T_{even}$  for execution instead of macro, the overheads (context saving and other actions on function call and return) take

Marros and functions are used in C programs. Functions are used when the codes should be compiled

only some However, on calling a function, the processor has to save the context, and on return,

note the applicat. Macros are used when short functional codes are to be inserted in a number of

7.4 PROGRAM ELEMENTS: DATA TYPES, DATA STRUCTURES, MODIFIERS, STATEMENTS, LOOPS AND POINTERS

# Use of Data Types

whenever data is named using an identifier, it will have the address(es) allocated at the memory Number of affocated addresses for data depends upon data type. For example, if a data-type long is

seclared for numTreks (number of ticks), then numTreks will be allocated 4 memory-addresses. at "byte. Most C compilers do not take a Boolean variable as data type. Then typedel is used to create a (64-bit) [Certain compilers do not take the "byte" as a data-type definition. The 'char' is then used instead Thebat, abort (16-bit), unsigned but (32-bit), but (32-bit), long double (64-bit) floor (32-bit) and double Boolean type variable in the C program. Embedded C compilers take a Boolean variable as data type. The 'C allows following primitive data types: char (8-bit) for characters, byte (8-bit), insigned short A data type appropriate for hardware is used. For example, a 16-bit timer can have only the unsigned

short-data type, and its range can be from 0 to 65535 only. process the declaration as unsigned byte for 8-bit port data. If 'unsigned character' can be used as a The typedef is also used. It is made clear by the following example. A compiler version may not

data-type then it can then be declared as follows: typeder unsigned character portAdata

\*define Pbyte portAdata 0xF1

# 7.4.2 Use of Modifiers

A modifier modifies the actions of a data type

eminimatigasi babbadari bne sigeano i galiministicis

boen mader han noblinged (bino3) S.Y slds I

all xabut na boa anten tahinabi oa yd aldiesaase inam nadw basu et il ylliasa baieraqu bine basu as na inamala nantab e navig ad oa et muante an't meren erane mon) ante arabut nomerano vaea to't salani na yd ytimabi It is a suracture with a series of elements, with each elebut distributed by any biddes and bottomer directly, but the tribot of tribot of the tribot of the tribot of tribot traducts are madve based at 11 about (OAF4) two rend of tenth detenon operation. An operation can be done only in the clement waiting for a read operation, which is called table of a drive amounts to eating a drive automitie a still

dentity by an index for easy operation. Index stars from

I is a surreture with a series of elements each having and the accessible by (

yet all associated back element is accessible by (

before the surreture of the surreture and the accessible of

or element of the etherune is to be given a distinct identity

by two or more indices for easy operation. The dimension

of an array equals far manber of indices that are needed to

distinctly telentify as array element. Indices surr from 0 and

are +ver integers. (An image fearner indices surreture)

are a very integers. (An image fearner is an array of pixels with

are the indices and

are a very integers. (An image fearner is an array of pixels with

are the indices and

are a very integers.)

Each element has a pointer to the next element Only dis-finst element to themtable by hastoo pointer Ulscader).

does it the other element is identifiable and hence is not accessible directly. By going favough the first element, and then consecutively through all the succeeding elements, an element can be read, read and deleted, can be added to a neighboring element, or replaced by another element. 801 is laxiq s insessigas llive drav 88 bits wot latroxirod

element is identifiable and hence is not accessable directly.

Proceeding continuously by traversing from the root element ment through all the succeeding daughtens, a tree element can be tread or read and deleted, or can be added to another dans read or read and deleted, or can be added to another can be read or read and deleted, or can be added to another the processes of the succession of the processes of the succession of the processes of t and it is done by the treetop pointer (header). No other not have daughters. Only the root element is identifiable having a daughter element. Each daughter element has two or more daughter element. The last one (leaf node) does or more daughter element. There is a root element. It has two or more branches each

pus sqr ar

folders, and so on. There is a file

ald radio to radmun a and rabio? a number of file folders. Each f.

yu examble is a directory. It has

tive. Each tesk has pointer of next task. Another example, i

A series of tasks which are

[88,801] bxiq amed agenu

Consider a pixel in an image thame. Consider Quarter-(1) image pixel in 144 × 176 = x

toansi to krusm a gailbraH O xəbni thiw təəldus ədi ni as

one adi bangiasa si 4 xabin driva

Maximum marks to the adject [9] sem shem - [4] sem shem

(9) Yaklas Auslas abnom tenti

(0) yeales \* 11 = yeales leso]

soli earny 51 at Vades beto.

OMIA S GROUP SS IL MULECONNI

page for to be seen toy de-

without [1 at blanch hene of a stream of byes

10 (s) plants

Note:  $^{8}$ puxel [0,0] represents the pixel at the left corner on top and pixel [144, 176] to the pixel at the right pixels (10.108, 88] to a pixel data element in a three-dimensional array form. It represents pixels position (108 × 88) in the  $10^{10}$  frame. a maximum of two daughters (branches) to each element. elements arranged in branches. A binary tree is a tree with daughter or replaced by another element. A tree has data

2.5 oldmox3

becatives were to an encounter, it services a function block, means that they is little allocation for the security of a new total property of the function of the function of the security of

### 2.4.3 Use of Pointers and Null Pointers

a reference to a starting metor a subfress. A pointer can refer to a variable, data structure or function, that we consider a pointer for example, unsigned o'but v 5 051000 means that we've seems of the constraint of the constra Paraters are powerful tools when used correctly and according to certain basic principles. A pointer is

I suewbued novig a m sau m ton at test toottast to beginn VMCH Laurence speciated the tenth of the superstance MLRT (Lord ) 0x0000. (We can assign any address a spaces of a for at the address 0x1000

### side Table and Hash Table 7.4.4 Use of Data Structures: Stack, Queue, Array, List, Tree, Pipe,

A data with the solid from the first of expensions and the solid solid from the solid from the solid solid

sed way Similarly, when there is a large amount of data, it must be organised different subjects studied in a semester are put in a proper table. The table in the markaheet shows to are stack, one dissentional array, queue, then queue, phys, a table (two-dimensional species and that bot example, the marks (or grades) of a student in the defresses as an organised way. Any data structure element can be retrieved Few important data

Table 7.2 summarises the uses and show exemplary uses of queues, stacks, arrays, lists and trees

Table 7.2 Uses of the various data structures in a program element

(1) Pushing of variables on inter-rupt or call to snother function

axii xij fe (s)ajdinās j

to a contexage a.A. and respective to a principle of a relation of the second of the context of the second of the context of the context of the context second of the context of the conte